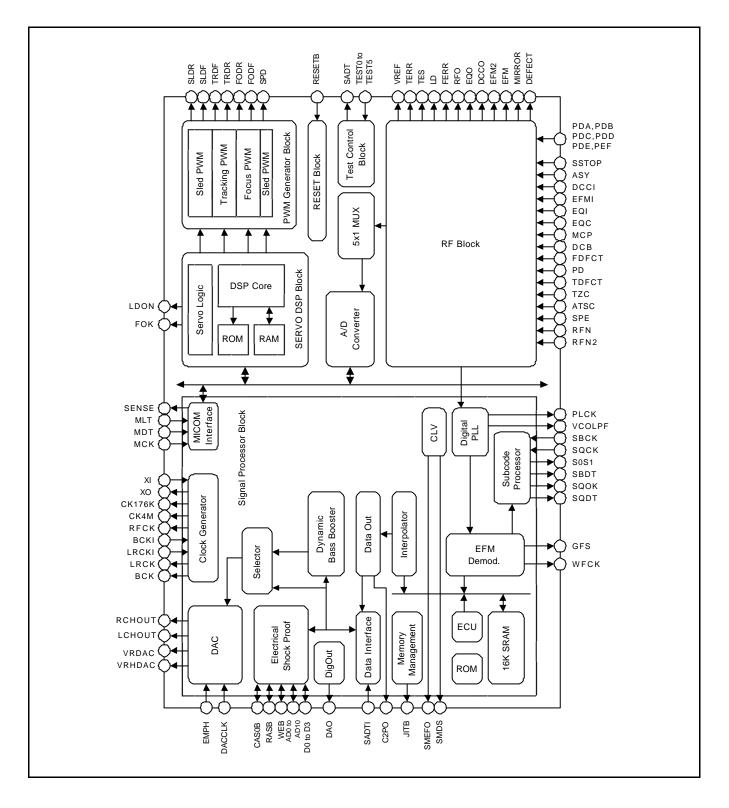

# DESCRIPTION

The S5L9232 is a one-chip LSI for Compact Disc Players including a CMOS RF, Digital Servo, CD digital signal processor, Dynamic Bass Boost, Sigma-Delta D/A converter, and Shock-proof memory controller.

## FEATURES

The S5L9232 has the following features:

- CMOS RF block

- Supports CD-RW (Re-Writable) Disc read

- RF Summing Amplifier

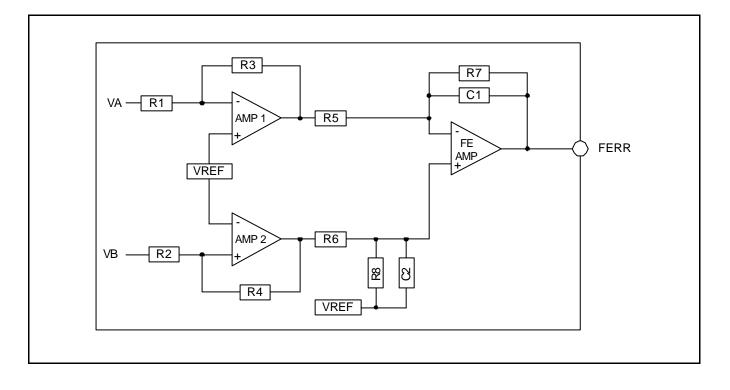

- Focus Error Amplifier

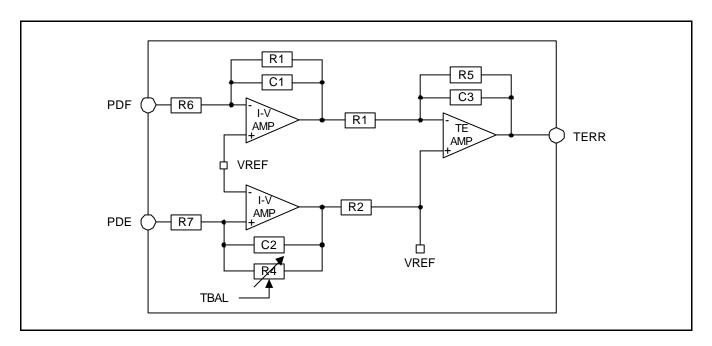

- Tracking Error Amplifier

- Automatic Focus/Tracking Balance Adjustment

- Automatic Focus/Tracking Gain Adjustment

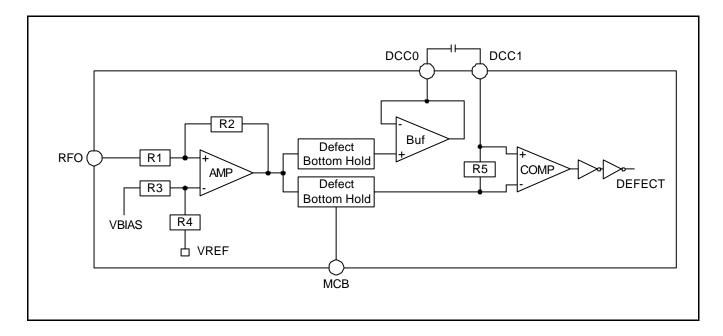

- Defect Detection

- Mirror Detection

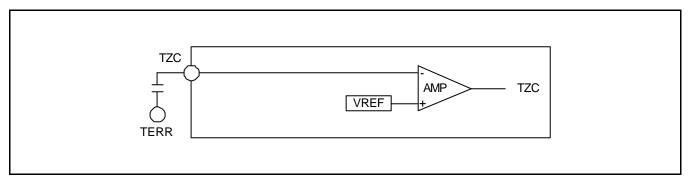

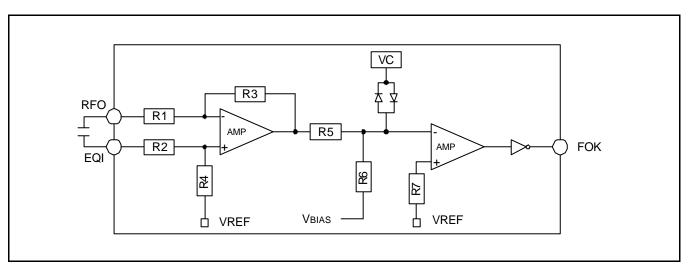

- Focus OK Detection

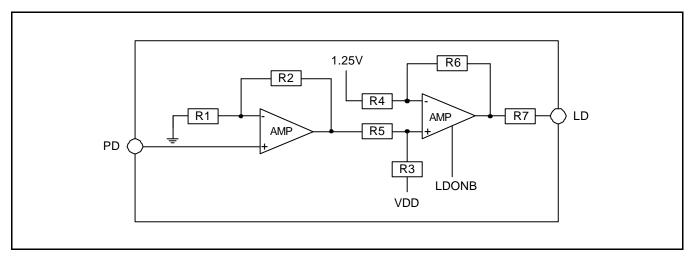

- Automatic Laser Diode Power Control

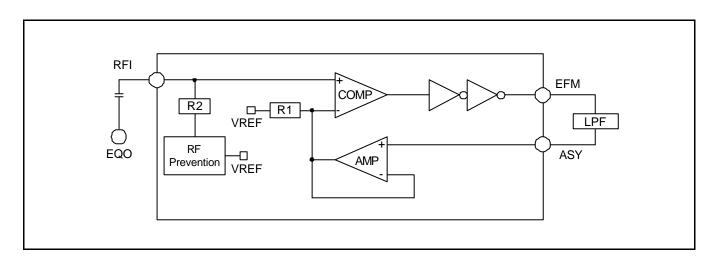

- EFM Comparator

- Anti-Shock Function

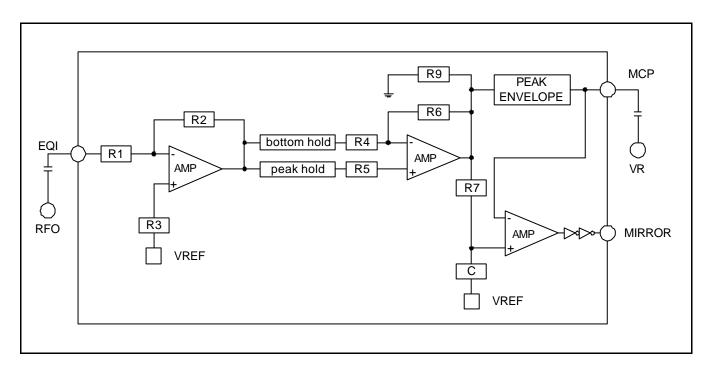

- RF AGC and EQ control

- Digital Servo block

- Focus, Tracking, Sled, Spindle Servo

- Focus/Tracking Offset Control

- Focus/Tracking Input Gain Control

- Focus Bias Control

- Tracking Balance Control

- Focus/Tracking Loop Gain Control

- Built-in Digital Signal Processor

- Drop Out and Shock countermeasure

- Filter coefficients can be changed by MICRO-CONTROLLER

- Built-in 8bit A/D and PWM output

- CDDSP, ESP, Audio DAC

- 1X and 2X play support

- C1: 2 error correction, C2: 2 error, 4 erasure correction

- Wide capture range playback mode

- EFM Data Demodulation

- Built-in Frame Sync Detection, Protection, and Insertion circuits

- Subcode Data Serial output

- Digital audio out

- Built-in ESP controller

- Built-in Sigma-Delta DAC & Audio Post-Filter

- Supports 2.4 3.6 Power Supply

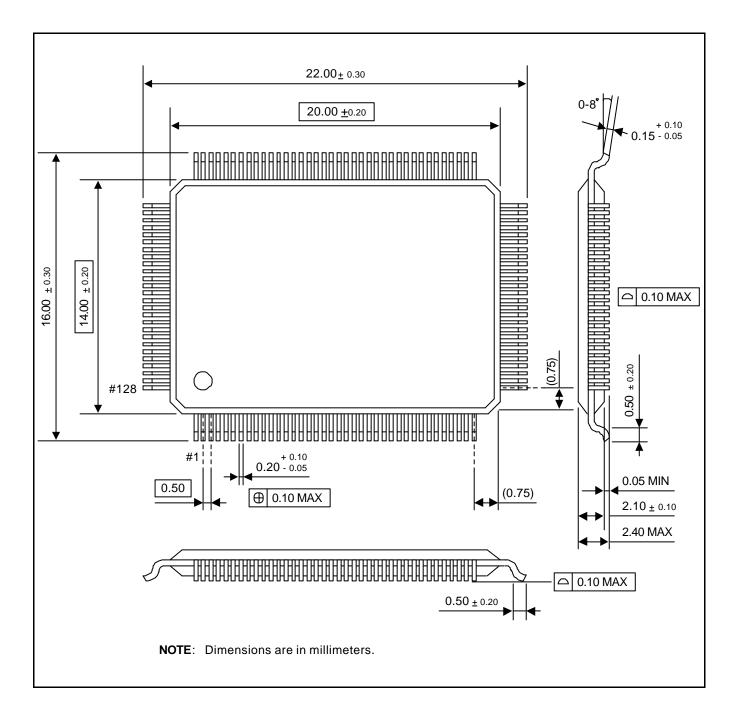

## **ORDERING INFORMATION**

| Device  | Package      | Operating Temperature |  |  |

|---------|--------------|-----------------------|--|--|

| S5L9232 | 128-QFP-1420 | -20 — 85°C            |  |  |

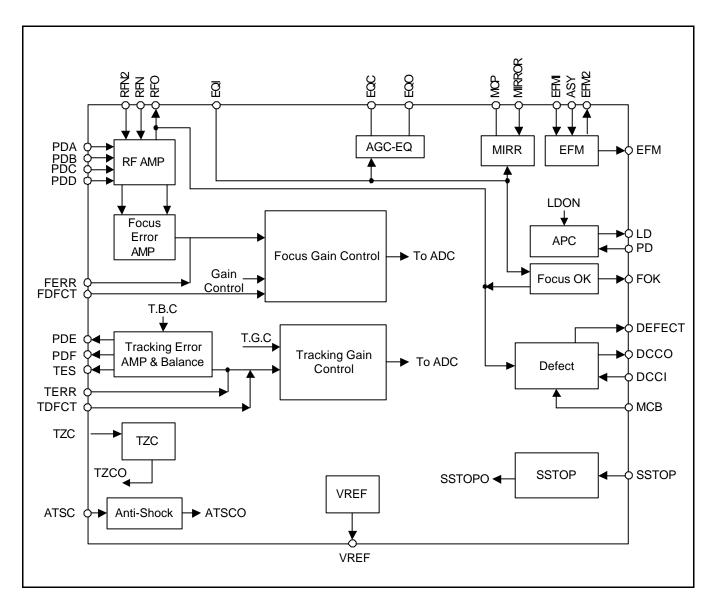

## **BLOCK DIAGRAM**

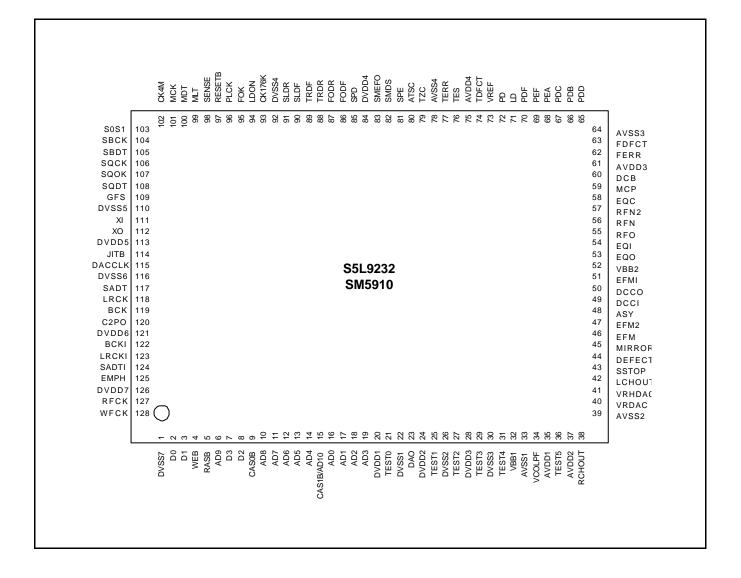

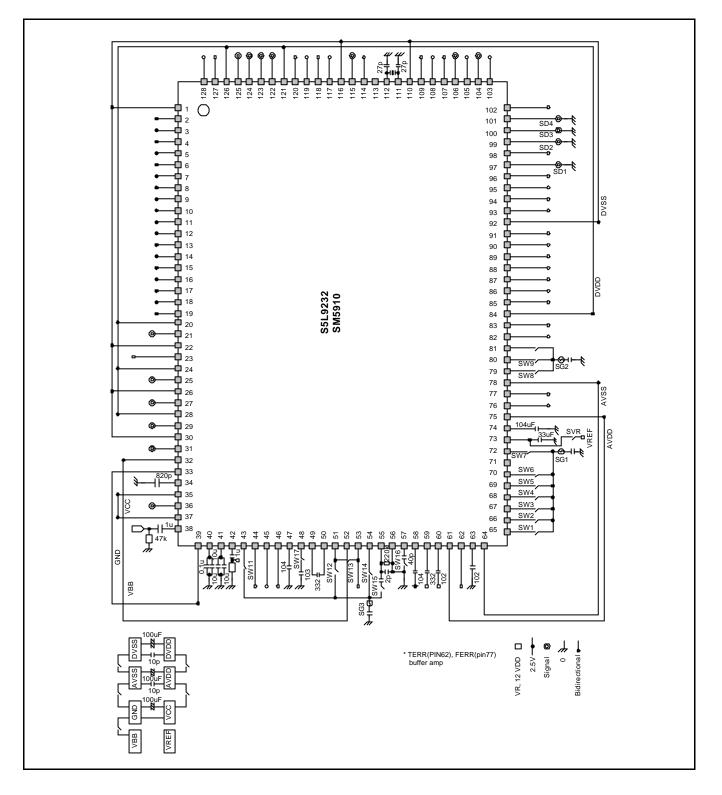

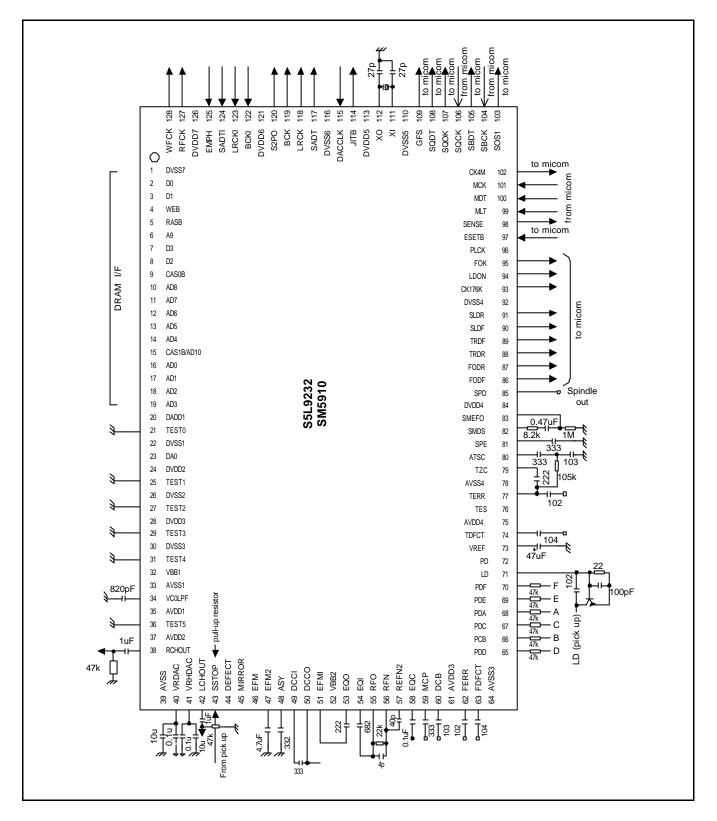

# **PIN CONFIGURATION**

# S5L9232(SM5910) PIN DESCRIPTIONS (128QFP)

| No | Pin Name    | I/O | Descriptions                                       | Note |

|----|-------------|-----|----------------------------------------------------|------|

| 1  | DVSS7       |     | Digital VSS (I/O PAD)                              |      |

| 2  | D0          | I/O | DRAM data Input/Output 0                           |      |

| 3  | D1          | I/O | DRAM data Input/Output 1                           |      |

| 4  | WEB         | I/O | DRAM Write Enable output. Active Low               |      |

| 5  | RASB        | I/O | DRAM Row Address Selection output. Active Low      |      |

| 6  | AD9         | I/O | DRAM Address output 9                              |      |

| 7  | D3          | I/O | DRAM data Input/Output 3                           |      |

| 8  | D2          | I/O | DRAM data Input/Output 2                           |      |

| 9  | CAS0B       | I/O | DRAM Column Address Selection output 0. Active Low |      |

| 10 | AD8         | I/O | DRAM Address output 8                              |      |

| 11 | AD7         | I/O | DRAM Address output 7                              |      |

| 12 | AD6         | I/O | DRAM Address output 6                              |      |

| 13 | AD5         | I/O | DRAM Address output 5                              |      |

| 14 | AD4         | I/O | DRAM Address output 4                              |      |

| 15 | CAS1B /AD10 | I/O | DRAM Column Address Selection output 1. Active Low |      |

| 16 | AD0         | I/O | DRAM Address output 0                              |      |

| 17 | AD1         | I/O | DRAM Address output 1                              |      |

| 18 | AD2         | I/O | DRAM Address output 2                              |      |

| 19 | AD3         | I/O | DRAM Address output 3                              |      |

| 20 | DVDD1       |     | Digital VDD (SERVO,CDDSP,ESP)                      |      |

| 21 | TEST0       | Ι   | Test mode selection 0 (for ESP & DBB). Active High |      |

| 22 | DVSS1       |     | Digital VSS (SERVO,CDDSP,ESP)                      |      |

| 23 | DAO         | 0   | Digital audio output                               |      |

| 24 | DVDD2       |     | Digital VDD (PLL)                                  |      |

| 25 | TEST1       | Ι   | Test mode selection 1. Active High                 |      |

| 26 | DVSS2       |     | Digital VSS (PLL)                                  |      |

| 27 | TEST2       | Ι   | Test mode selection 2. Active High                 |      |

| 28 | DVDD3       |     | Digital VDD (Sigma-Delta DAC,ADC)                  |      |

| 29 | TEST3       | Ι   | Test mode selection 3. Active High                 |      |

| 30 | DVSS3       |     | Digital VSS (Sigma-Delta DAC,ADC)                  |      |

| 31 | TEST4       | Ι   | Test mode selection 4. Active High                 |      |

| 32 | VBB1        |     | VSS for Bulk Bias (PLL)                            |      |

# S5L9232(SM5910) PIN DESCRIPTIONS (128QFP) (Continued)

| No | Pin Name | I/O | Descriptions                                | Note |

|----|----------|-----|---------------------------------------------|------|

| 33 | AVSS1    |     | Analog VSS (PLL)                            |      |

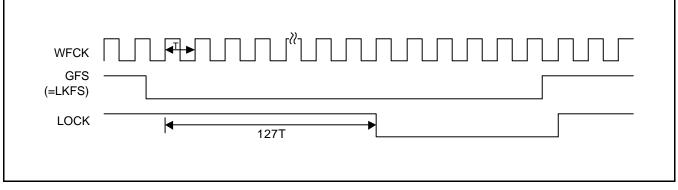

| 34 | VCOLPF   | 0   | Pump out for VCO                            |      |

| 35 | AVDD1    |     | Analog VDD (PLL)                            |      |

| 36 | TEST5    | I   | Test mode selection 5. Active High          |      |

| 37 | AVDD2    |     | Analog VDD (Sigma-Delta DAC)                |      |

| 38 | RCHOUT   | 0   | Right-channel audio output                  |      |

| 39 | AVSS2    |     | Analog VSS (Sigma-Delta DAC)                |      |

| 40 | VRDAC    | 0   | Voltage reference for Sigma-Delta DAC       |      |

| 41 | VRHDAC   | 0   | Half voltage reference for Sigma-Delta DAC  |      |

| 42 | LCHOUT   | 0   | Left-channel audio output                   |      |

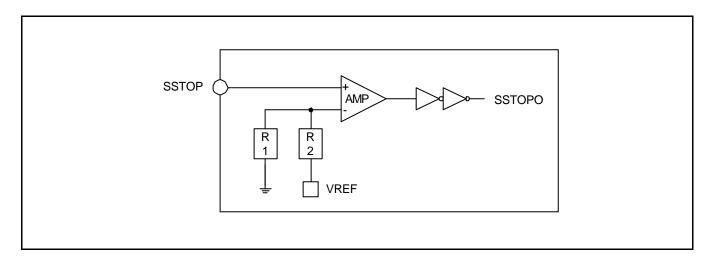

| 43 | SSTOP    | I   | SSTOP input (internal 47k $\Omega$ pull-up) |      |

| 44 | DEFECT   | 0   | Defect Output                               |      |

| 45 | MIRROR   | 0   | Mirror output                               |      |

| 46 | EFM      | 0   | EFM output                                  |      |

| 47 | EFM2     | 0   | EFM output2 (through resistor)              |      |

| 48 | ASY      | I   | LPF connection for EFM slicer               |      |

| 49 | DCCI     | I   | Defect bottom hold capacitor                |      |

| 50 | DCCO     | 0   | Defect bottom hold output                   |      |

| 51 | EFMI     | I   | EFM input                                   |      |

| 52 | VBB2     |     | VSS for Bulk Bias (ADC, Sigma-Delta DAC)    |      |

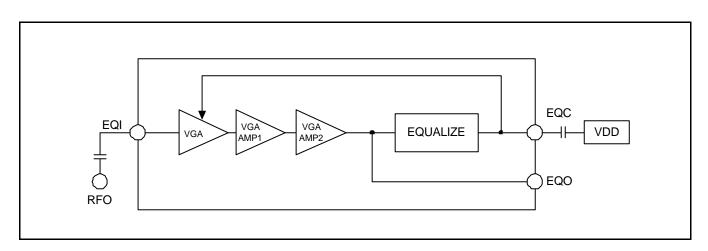

| 53 | EQO      | 0   | AGC-EQ output                               |      |

| 54 | EQI      | I   | AGC-EQ input coupling capacitor             |      |

| 55 | RFO      | 0   | RF summing output                           |      |

| 56 | RFN      | I   | RF summing AMP (-) input                    |      |

| 57 | RFN2     | I   | RF summing AMP (-) input for 2X Filter      |      |

| 58 | EQC      | I   | AGC-EQ capacitor                            |      |

| 59 | MCP      | I   | Mirror hold capacitor                       |      |

| 60 | DCB      | I   | Defect bottom hold capacitor                |      |

| 61 | AVDD3    |     | Analog VDD (RF)                             |      |

| 62 | FERR     | 0   | Focus error output                          |      |

| 63 | FDFCT    | 0   | Focus error LPF                             |      |

| 64 | AVSS3    |     | Analog VSS (RF)                             |      |

| 65 | PDD      | Ι   | RF I-V AMP D input from pick-up             |      |

# S5L9232(SM5910) PIN DESCRIPTIONS (128QFP) (Continued)

| No | Pin Name | I/O | Descriptions                                                 | Note |

|----|----------|-----|--------------------------------------------------------------|------|

| 66 | PDB      | I   | RF I-V AMP B input from pick-up                              |      |

| 67 | PDC      | I   | RF I-V AMP C input from pick-up                              |      |

| 68 | PDA      | I   | RF I-V AMP A input from pick-up                              |      |

| 69 | PDE      | I   | E I-V AMP input from pick-up                                 |      |

| 70 | PDF      | I   | F I-V AMP input from pick-up                                 |      |

| 71 | LD       | 0   | APC output                                                   |      |

| 72 | PD       | I   | APC input                                                    |      |

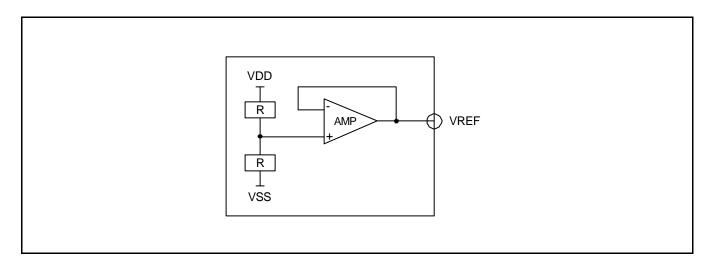

| 73 | VREF     | 0   | AVDD/2 DC voltage output                                     |      |

| 74 | TDFCT    | 0   | Tracking error LPF                                           |      |

| 75 | AVDD4    |     | Analog VDD (ADC)                                             |      |

| 76 | TES      | 0   | Tracking Summing output                                      |      |

| 77 | TERR     | 0   | Tracking error output                                        |      |

| 78 | AVSS4    |     | Analog VSS (ADC)                                             |      |

| 79 | TZC      | I   | Tracking zero cross input                                    |      |

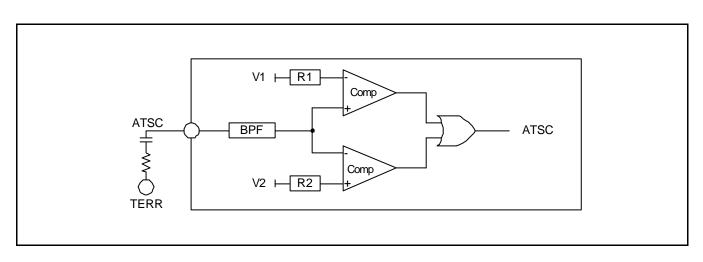

| 80 | ATSC     | I   | Anti-shock input from BPF                                    |      |

| 81 | SPE      | I   | Spindle error input                                          |      |

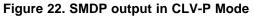

| 82 | SMDS     | 0   | Spindle motor velocity control in Phase Mode                 |      |

| 83 | SMEFO    | 0   | CLV LPF connection                                           |      |

| 84 | DVDD4    |     | Digital VDD (SERVO,CDDSP,ESP)                                |      |

| 85 | SPD      | 0   | Spindle servo output. 3-state                                |      |

| 86 | FODF     | 0   | Focus servo Forward output                                   |      |

| 87 | FODR     | 0   | Focus servo Reverse output                                   |      |

| 88 | TRDR     | 0   | Tracking servo Reverse output                                |      |

| 89 | TRDF     | 0   | Tracking servo Forward output                                |      |

| 90 | SLDF     | 0   | Sled servo Forward output                                    |      |

| 91 | SLDR     | 0   | Sled servo Reverse output                                    |      |

| 92 | DVSS4    |     | Digital VSS (SERVO,CDDSP,ESP)                                |      |

| 93 | CK176K   | 0   | 176.4kHz(16.9344MHz/96) output (X'tal divided))              |      |

| 94 | LDON     | 0   | LDON Status output. Active High                              |      |

| 95 | FOK      | 0   | Focus OK output. Active High                                 |      |

| 96 | PLCK     | 0   | 4.3218MHz output(1X)<br>8.6436MHz output (2X). (VCO divided) |      |

| 97 | RESETB   | I   | MICRO-CONTROLLER reset. Active Low                           |      |

# S5L9232(SM5910) PIN DESCRIPTIONS (128QFP) (Continued)

| No  | Pin Name | I/O | Descriptions                                                      | Note |

|-----|----------|-----|-------------------------------------------------------------------|------|

| 98  | SENSE    | 0   | Internal status monitor.                                          |      |

| 99  | MLT      | I   | MICRO-CONTROLLER serial data latching signal input.<br>Active Low |      |

| 100 | MDT      | I   | MICRO-CONTROLLER data input                                       |      |

| 101 | MCK      | I   | MICRO-CONTROLLER clock signal input                               |      |

| 102 | CK4M     | 0   | 4.2336MHz/16.9344MHz output(X'tal divided)                        |      |

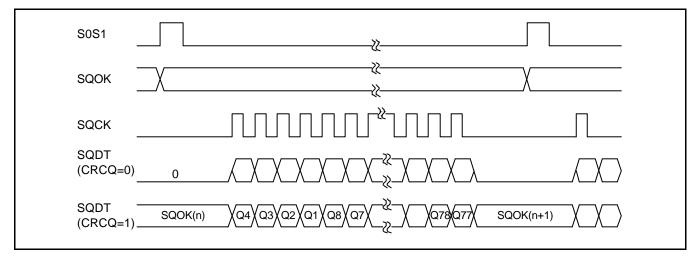

| 103 | SOS1     | 0   | Subcode SYNC S0+S1 output                                         |      |

| 104 | SBCK     | I   | Subcode data bit clock input                                      |      |

| 105 | SBDT     | 0   | Subcode data serial output                                        |      |

| 106 | SQCK     | I   | Subcode-Q data bit clock                                          |      |

| 107 | SQOK     | 0   | Subcode-Q CRC check result signal                                 |      |

| 108 | SQDT     | 0   | Subcode-Q data serial output                                      |      |

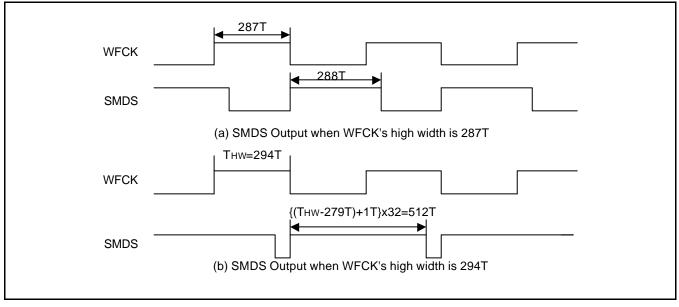

| 109 | GFS      | 0   | Lock status output of Frame Sync                                  |      |

| 110 | DVSS5    |     | Digital VSS (I/O PAD)                                             |      |

| 111 | XI       | I   | System clock input (16.9344MHz)                                   |      |

| 112 | XO       | 0   | System clock output                                               |      |

| 113 | DVDD5    |     | Digital VDD (I/O PAD)                                             |      |

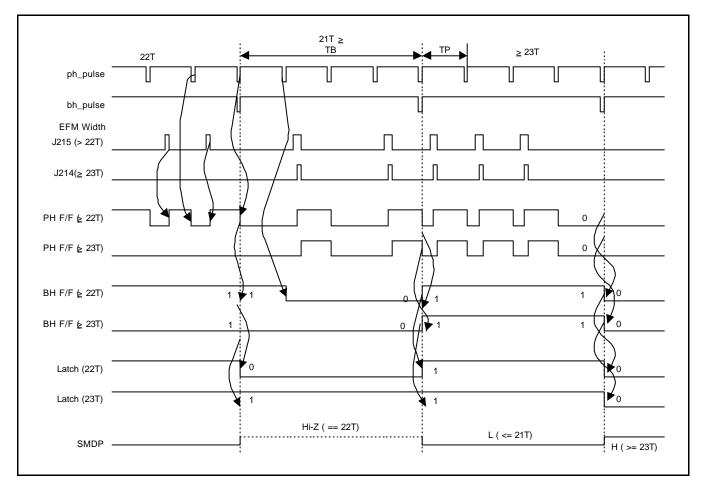

| 114 | JITB     | 0   | Jitter margin flag. Active Low                                    |      |

| 115 | DACCLK   | I   | Sigma-Delta DAC system clock input                                |      |

| 116 | DVSS6    |     | Digital VSS (SERVO,CDDSP,ESP)                                     |      |

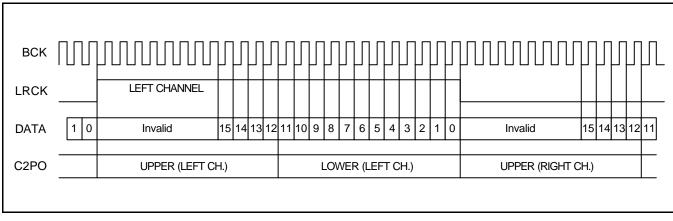

| 117 | SADT     | 0   | Serial audio data output                                          |      |

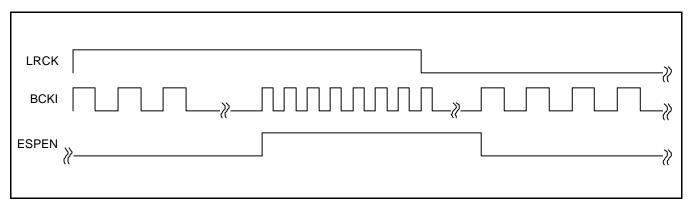

| 118 | LRCK     | 0   | Channel clock output                                              |      |

| 119 | BCK      | 0   | Serial audio data bit clock output                                |      |

| 120 | C2PO     | 0   | C2 pointer for serial audio data                                  |      |

| 121 | DVDD6    |     | Digital VDD (SERVO,CDDSP,ESP)                                     |      |

| 122 | BCKI     | I   | Serial data bit clock input                                       |      |

| 123 | LRCKI    | Ι   | Channel clock input                                               |      |

| 124 | SADTI    | Ι   | Serial audio data input                                           |      |

| 125 | EMPH     | Ι   | Emphasis/non-emphasis output. H: emphasis                         |      |

| 126 | DVDD7    |     | Digital VDD (I/O PAD)                                             |      |

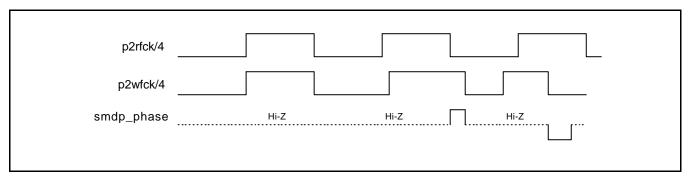

| 127 | RFCK     | 0   | X'tal controlled read frame clock                                 |      |

| 128 | WFCK     | 0   | VCO controlled write frame clock                                  |      |

# **ABSOLUTE MAXIMUM RATINGS**

| No | Item                  | Symbol           | Spec.                  | Unit |

|----|-----------------------|------------------|------------------------|------|

| 1  | Supply Voltage        | V <sub>DD</sub>  | -0.15 — 3.8            | V    |

| 2  | Input Voltage         | Vı               | -0.15 to $V_{DD+0.15}$ | V    |

| 3  | Output Voltage        | Vo               | -0.15 — 3.8            | V    |

| 4  | Operating Temperature | T <sub>OPR</sub> | -20 — 85               | °C   |

| 5  | Storage Temperature   | T <sub>STG</sub> | -40 — 125              | °C   |

| 6  | Power Dissipation     | P <sub>D</sub>   | 500                    | mW   |

## **RECOMMENDED OPERATING CONDITIONS**

| Characteristics | Symbol          | Min | Тур | Max | Unit |

|-----------------|-----------------|-----|-----|-----|------|

| Supply Voltage  | V <sub>DD</sub> | 2.4 | 3.0 | 3.6 | V    |

| Operating Temp. | Topr            | -20 | 25  | 85  | °C   |

# **ELECTRICAL CHARACTERISTICS**

#### LOGIC' S

#### **DC Characteristics:**

(V<sub>DD</sub> = 2.5, VSS = 0V, Ta = 25°C)

| No | Item                                     | Symbol              | Cond.                             | Min | Тур | Мах | Unit | Misc.  |

|----|------------------------------------------|---------------------|-----------------------------------|-----|-----|-----|------|--------|

| 1  | 'H' Input Voltage1                       | V <sub>IH(1)</sub>  |                                   | 1.7 | -   | -   | V    | note 1 |

| 2  | 'L' Input Voltage1                       | V <sub>IL(1)</sub>  |                                   | -   | -   | 0.7 | V    |        |

| 3  | 'H' Input Voltage2                       | V <sub>IH(2)</sub>  |                                   | -   | -   | 1.9 | V    | note 2 |

| 4  | 'L' Input Voltage2                       | V <sub>IL(2)</sub>  |                                   | 0.6 | -   | -   | V    |        |

| 5  | 'H' Output Voltage1                      | V <sub>OH(1)</sub>  | I <sub>OH</sub> = -2mA            | 1.9 | -   | -   | V    | note 3 |

| 6  | 'L' Output Voltage1                      | V <sub>OL(1)</sub>  | I <sub>OL</sub> = 2mA             | -   | -   | 0.5 | V    |        |

| 7  | Three State Output<br>Leak Current       | I <sub>O(LKG)</sub> | $V_{O} = 0 - V_{DD}$              | -10 | -   | 10  | uA   | note 4 |

| 8  | Current Consumption                      | I <sub>DD</sub>     | note 5                            |     | 35  |     | mA   |        |

| 9  | Low Level Input Current for with Pull-up | I <sub>IL</sub>     | V <sub>IN</sub> = V <sub>SS</sub> |     | 33  |     | uA   | note6  |

#### NOTES:

- 1. Related pins: CMOS interface.

- 2. Related pins: CMOS Schmitt trigger interface, (MLT, MCK, MDT, RESETB pins).

- 3. Related pins: All output pins except #112(XO). Related pins: SMEFO (#83), SMDS (#82), SENSE (#98), and SPD (#85) All  $V_{DD}$ = 2.5, All  $V_{SS}$ = 0V, XI(#111) = 16.9344MHz

- 6. Related pins : All Bi-directional Pins.  $V_{DD}$ = 3.3 V condition.

#### <Pin Summary>

| 1 | Pin Function | Clock Input/Output Pin                                                                                                                             |

|---|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Pin Name     | XI/XO                                                                                                                                              |

| 2 | Pin Function | Schmitt Input Pins                                                                                                                                 |

|   | Pin Name     | RESETB, MLT, MDT, MCK                                                                                                                              |

| 3 | Pin Function | I/O Pins (Tri-state bi-directional buffer with Pull-up)                                                                                            |

|   | Pin Name     | D0, D1, D2, D3, WEB, RASB, CAS0B, AD0, AD1, AD2, AD3, AD4, AD5, AD6, AD7, AD8, AD9, AD10                                                           |

| 4 | Pin Function | Input Pins (Digital)                                                                                                                               |

|   | Pin Name     | TEST0, TEST1, TEST2, TEST3, TEST4, SBCK, SQCK, DACCLK, BCKI, LRCKI, SADTI, EMPH                                                                    |

| 5 | Pin Function | Input Pins (Analog)                                                                                                                                |

|   | Pin Name     | TEST5, SSTOP, ASY, DCCI, EFMI, EQI, RFN, RFN2, EQC, MPC, DCB, FDFCT, PDD, PDB, PDC, PDA, PDE, PDF, PD, TDFCT, TZC, ATSC, SPE                       |

| 6 | Pin Function | Output Pins (Digital)                                                                                                                              |

|   | Pin Name     | DAO, FODF, FODR, TRDR, TRDF, SLDF, SLDR, CK176K, LDON, FOK,<br>PLCK, CK4M, S0S1, SBDT, SQOK, SQDT, GFS, JITB, SADT, LRCK, BCK,<br>C2PO, RFCK, WFCK |

| 7 | Pin Function | Output Pins (Tri-state)                                                                                                                            |

|   | Pin Name     | SMDS, SMEFO, SPD, SENSE                                                                                                                            |

| 8 | Pin Function | Output Pins (Analog)                                                                                                                               |

|   | Pin Name     | VCOLPF, RCHOUT, VRDAC, VRHDAC, LCHOUT, DEFECT, MIRROR, EFM, EFM2, DCCO, EQO, RFO, FERR, LD, VREF, TES, TERR                                        |

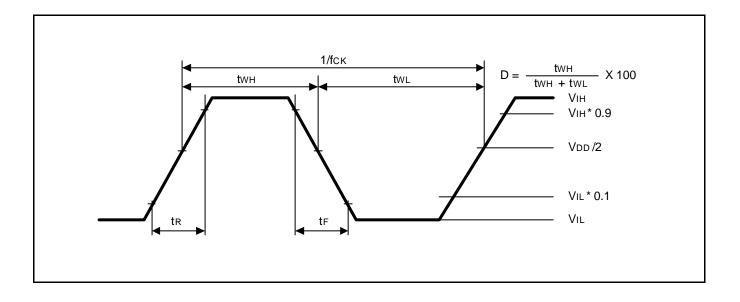

## AC Characteristics:

When a pulse is input into XI pin:

$(V_{DD} = 2.5V, V_{SS} = 0V, Ta = 25^{\circ}C)$

| No | ltem                  | Symbol                          | Min                  | Тур     | Max | Unit |

|----|-----------------------|---------------------------------|----------------------|---------|-----|------|

| 1  | Clock Frequency       | fск                             | -                    | 16.9344 | -   | MHz  |

| 2  | Clock Duty            | D                               | -                    | 50      | -   | %    |

| 3  | Input 'H' Level       | V <sub>IH</sub>                 | V <sub>DD</sub> -0.7 | -       | -   | V    |

| 4  | Input 'L' Level       | VL                              | -                    | -       | 0.7 | V    |

| 5  | Rising & Falling Time | t <sub>R</sub> , t <sub>F</sub> | -                    | -       | 8   | ns   |

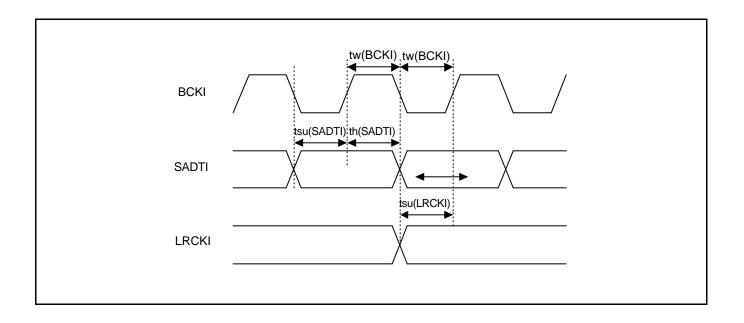

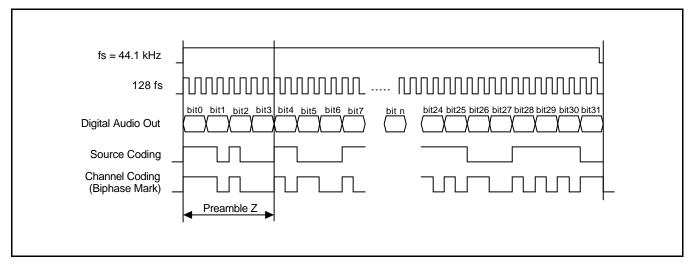

# BCKI, LRCKI, and SADTI (Same as BCK, LRCK, SADT Output) :

$(V_{DD}= 2.5V \pm 5\%, V_{SS}= 0V, Ta = -20 - 85^{\circ}C)$

| ltem             | Symbol | Condition | Min. | Тур.     | Max. | Unit |

|------------------|--------|-----------|------|----------|------|------|

| BCKI pulse width | tw     |           |      | 1/(96fs) |      | ns   |

| SADTI setup time | tsu    |           | 20   |          |      | ns   |

| SADTI hold time  | th     |           | 20   |          |      | ns   |

| LRCKI setup time | tsu    |           | 20   |          |      | ns   |

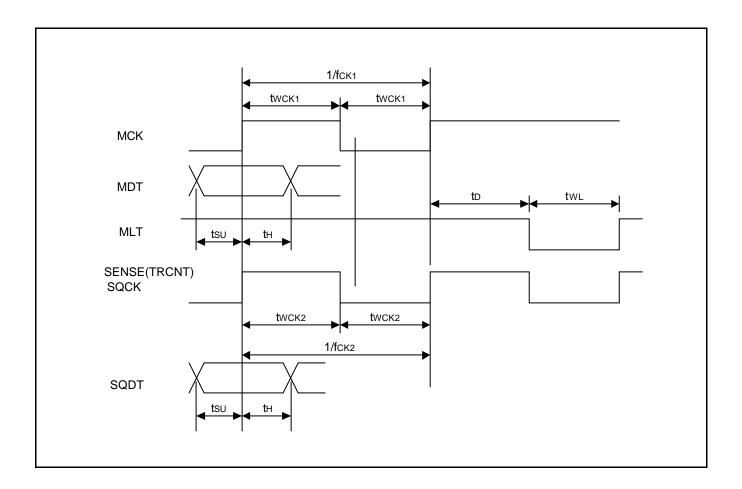

# MCK, MDT, MLT

$(V_{DD} = 2.5, VSS = 0V, Ta = 25^{\circ}C)$

| No | ltem                            | Symbol            | Min | Тур | Max | Unit |

|----|---------------------------------|-------------------|-----|-----|-----|------|

| 1  | Clock Frequency                 | f <sub>СК1</sub>  | -   | -   | 8   | MHz  |

| 2  | Clock Pulse Width               | t <sub>WCK1</sub> | 500 | -   | -   | ns   |

| 3  | Setup Time                      | t <sub>SU</sub>   | 300 | -   | -   | ns   |

| 4  | Hold Time                       | t <sub>H</sub>    | 300 | -   | -   | ns   |

| 5  | Delay Time                      | t <sub>D</sub>    | 300 | -   | -   | ns   |

| 6  | Latch Pulse Width               | t <sub>WL</sub>   | 500 | -   | -   | ns   |

| 7  | SENSE (TRCNT), SQCK Frequency   | f <sub>CK2</sub>  | -   | -   | 1   | MHz  |

| 8  | SENSE (TRCNT), SQCK Pulse Width | t <sub>WCK2</sub> | 500 | -   | -   | ns   |

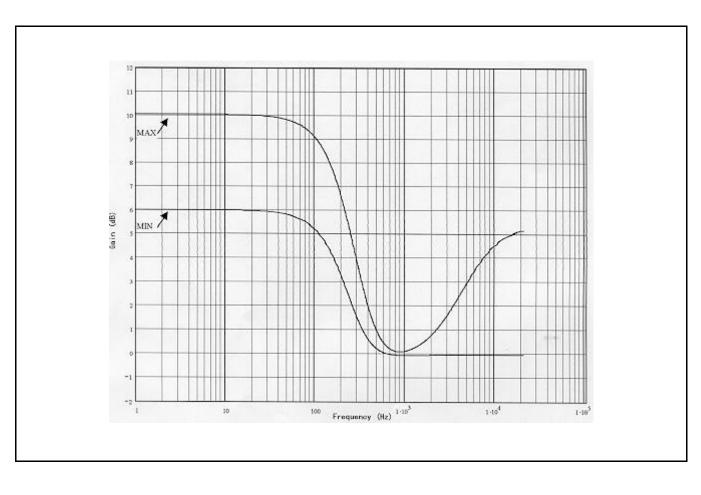

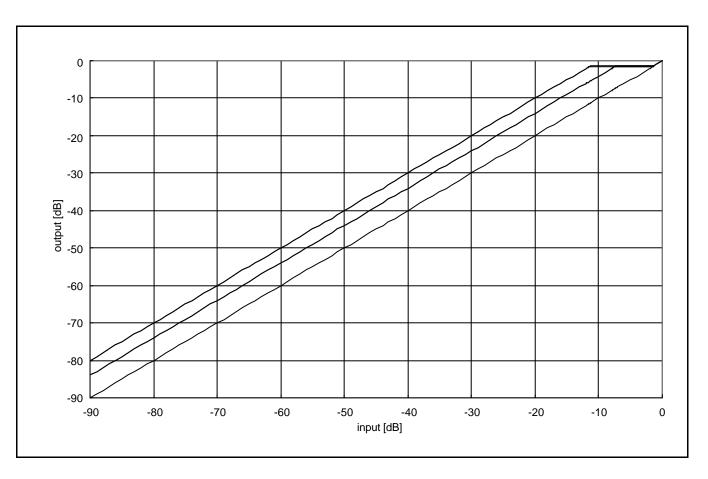

#### SIGMA-DELTA AUDIO DAC

(V<sub>DDD</sub>,V<sub>DDA</sub> = 2.5V, Temp=25°C, Fs = 44.1kHz, Signal Frequency=20 — 20kHz, Cload of AoutL, AoutR = 10pF)

| Parameter                           | Min | Тур                  | Max   | Units |

|-------------------------------------|-----|----------------------|-------|-------|

| Resolution                          |     | 16                   |       | bits  |

| SNR <sup>&lt;1&gt;</sup>            | 92  |                      |       | dB    |

| THD <sup>&lt;2&gt;</sup>            |     | 0.007                |       | %     |

| SND(THD+Noise) <sup>&lt;3&gt;</sup> |     | 82                   |       | dB    |

| Dynamic Range <sup>&lt;4&gt;</sup>  | 92  |                      |       | dB    |

| Reference Voltage Output            |     | $0.5 	imes V_{DDA}$  |       | V     |

| Frequency Response                  |     | ± 0.1                | ± 0.5 | dB    |

| Analog Output                       |     |                      |       |       |

| Voltage Range                       |     | $0.75 	imes V_{DDA}$ |       | Vpp   |

| Load Impedance                      | 10K |                      |       | Ω     |

#### NOTES:

1. 1kHz 0dB Sine wave Input, EIAJ

2. 1kHz -3dB Sine wave Input

3. 1kHz 0dB Sine wave Input, (Not EIAJ)

4. 1kHz -60dB Sine wave Input, and then measured data + 60dB

# **PWM OUTPUT**

# FUNCTIONAL DESCRIPTIONS

## MICRO-CONTROLLER INTERFACE

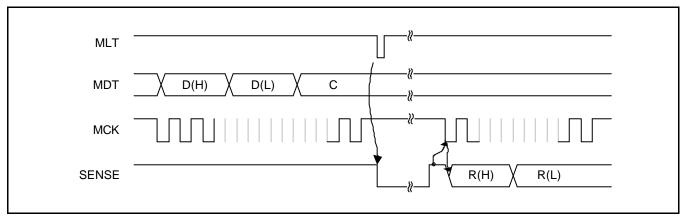

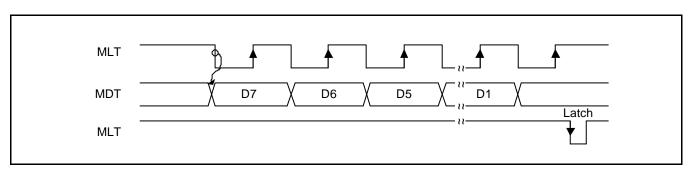

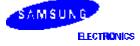

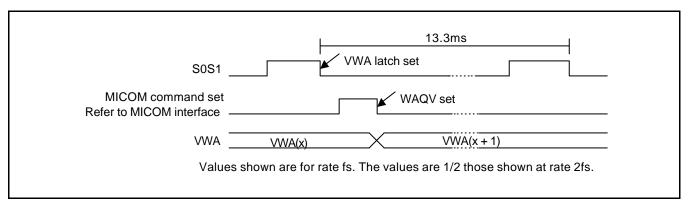

Data inputs from micro-controller are received through MDAT, and transmitted by MCK. This signal is stored in the Control Register by MLT. The Timing diagram for this process is shown in Figure 1. Each command is carried out by receiving data and commands (MSB first) from micro-controller.

Figure 1. Micro-controller Interface Timing Chart

For CD-DSP, the command and data length is 8 bits respectively. In the case of the Servo, the command length is fixed at 8 bits, but the data length is varied from 0 to16 bits. When Data is 16 bits and command is 8 bits, the input is made starting with the MSB in the following order: D(H) = D15 - D8, D(L) = D7 - D0, and C = C7 - C0. In the case of a command with no data, you only need to input the command byte. When data input is finished, a pulse at MLT is generated to indicate that the command transmission is finished. From then on, command is decoded and carried out. The SENSE output shows READY (/BUSY) status at default. In other words, it is "L" when it receives a command, and "H" when the command is completed. In certain commands, SENSE output has a meaning other than that of Ready. For example, it can show the "on/off" information of the limit switch or the presence of a disc.

The detailed input timing of S5L9232 is shown in Figure 2. Micro-controller sends MDT to MCK falling edge, in the order of MSB, Data, and Command. S5L9232 latches the data at MCK's rising edge. Micro-controller no longer sends MCK when the transmission of all MDT is finished. At this time, MLT becomes "L" to indicate that the transmission of command and data from Micro-controller to S5L9232 is complete.

Figure 2. Micro-controller to S5L9232 Input Timing

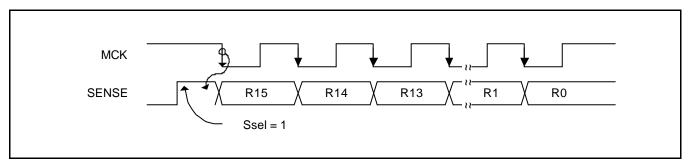

The timing for sending data to Micro-controller is shown in Figure 3. In such a case the Digital Servo Signal Processor (DSSP) stores the data to be sent to Micro-controller after command has been carried out, in the output buffer. At the same time, it makes the SENSE output "H" to indicate that the DSSP's command processing routine is finished. If Micro-controller needs to read the response data, only MCK is sent to S5L9232. S5L9232 then sends the output serially through SENSE to Micro-controller, at MCK's falling edge. Since SENSE's Ssel (Serial Data Select Signal) is "1", the data in the output buffer should be output. The output to SENSE is carried out in units of byte, and in the order of R(H) = R15 - R8 and R(L) = R7 - R0, starting with MSB.

Figure 3. S5L9232 to Micro-controller Output Timing

S5L9232 generates one SENSE signal that makes the CD-DSP and Servo into a single chip and goes through MUX to Micro-controller. Hence, Micro-controller can use SENSE as a direct input signal.

As shown in Table 1 and Table 2, Micro-controller command can be divided into Micro-controller command for Digital Servo (00 — 5Fh), and Micro-controller command for CD-DSP (60h — FFh)

#### S5L9232

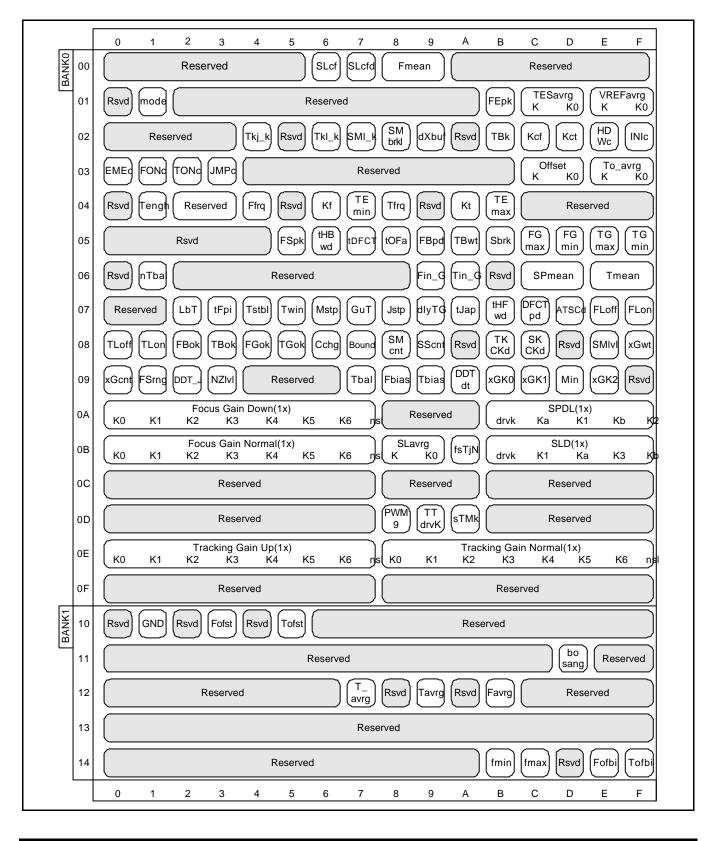

## MICRO-CONTROLLER COMMAND SET

| Addr. | CMD    | D15  | Data  |      |        |      |      |       |        |                 |       |  |  |  |

|-------|--------|------|-------|------|--------|------|------|-------|--------|-----------------|-------|--|--|--|

| 00    |        | 015  | D14   | D13  | D12    | D11  | D10  | D9    | D8     | Sense           | Value |  |  |  |

| 00    |        | D7   | D6    | D5   | D4     | D3   | D2   | D1    | D0     |                 |       |  |  |  |

|       | STPcmd |      |       |      |        |      |      |       |        | /BUSY           | -     |  |  |  |

|       |        |      |       |      |        | LDX  | IDLE | ABRT  | STOP   |                 |       |  |  |  |

| 01    | DDTcmd |      |       |      |        |      |      |       |        | *SERIAL<br>DATA | -     |  |  |  |

|       |        | AUTO | UPDN  | FIGA | FBAL   | RPT  | FSP2 | FSP1  | FSP0   |                 |       |  |  |  |

| 02    | FONcmd |      |       |      |        |      |      |       |        | /BUSY           | -     |  |  |  |

|       |        | LYRX | Fmthd | FOPI | FSPC   | PIL3 | PIL2 | PIL1  | PIL0   |                 |       |  |  |  |

| 03    | TONcmd |      |       |      |        |      |      |       |        | /BUSY           | -     |  |  |  |

|       |        |      | SLSV  |      | TOLB   | MTLB | SFOG | STRG  |        |                 |       |  |  |  |

| 04    | SLDcmd |      |       |      |        |      |      |       |        | /BUSY           | -     |  |  |  |

|       |        |      |       |      |        |      | SPLY | SMOV  | HOMEIN |                 |       |  |  |  |

| 05    | JMPcmd | DIR  | JPM1  | JPM0 | JIT2   | JIT1 | JIT0 | JPD9  | JPD8   | /BUSY           | -     |  |  |  |

|       |        | JPD7 | JPD6  | JPD5 | JPD4   | JPD3 | JPD2 | JPD1  | JPD0   |                 |       |  |  |  |

| 07    | EMEcmd |      |       |      |        |      |      |       |        | /BUSY           | 004Fh |  |  |  |

|       |        | TEST | SLST  |      | upFv   | dsAS | ASFO | ASTR  |        |                 |       |  |  |  |

| 08    | HDWcmd |      |       |      |        |      |      |       |        | /BUSY           | 0008h |  |  |  |

|       |        |      | SSTOP | LPDS | SPHOLD | PCUP |      | SLbrk | 0      |                 |       |  |  |  |

| 09    | INIcmd |      |       |      |        |      |      |       |        | /BUSY           | 0041h |  |  |  |

|       |        |      | JPCK  |      |        | BJJM | BTS  | enJaP | Slref  |                 |       |  |  |  |

| 0B    | SPDcmd |      |       |      |        |      |      |       |        | /BUSY           | 0000h |  |  |  |

|       |        |      |       |      |        |      |      |       | SPD    |                 |       |  |  |  |

| 11    | OFAcmd |      |       |      |        |      |      |       |        | /BUSY           | -     |  |  |  |

|       |        |      |       |      |        |      |      | LDoff | FTS    |                 |       |  |  |  |

| 12    | FBAcmd |      |       |      |        |      |      |       |        | /BUSY           | -     |  |  |  |

|       |        |      |       |      |        |      |      |       |        |                 |       |  |  |  |

| 13    | TBAcmd |      |       |      |        |      |      |       |        | /BUSY           | -     |  |  |  |

|       |        |      |       |      |        |      |      | RPTB  | TIGA   |                 |       |  |  |  |

| 14    | FGAcmd |      |       |      |        |      |      |       |        | /BUSY           | -     |  |  |  |

| 15    | TGAcmd |      |       |      |        |      |      |       |        | /BUSY           | -     |  |  |  |

## Table 1. Servo part MICRO-CONTROLLER command set

|       |              |            |        |        | Data |      |       |           |        |                     | INIT. |

|-------|--------------|------------|--------|--------|------|------|-------|-----------|--------|---------------------|-------|

| Addr. | CMD          | D15        | D14    | D13    | D12  | D11  | D10   | D9        | D8     | Sense               | Value |

|       |              | D7         | D6     | D5     | D4   | D3   | D2    | D1        | D0     |                     |       |

| 17    | RFSNS<br>cmd |            |        |        |      |      |       |           |        | **SIGNAL<br>MONITOR | 0000h |

|       |              |            |        |        |      |      | SEN2  | SEN1      | SEN0   |                     |       |

| 18    | SQDTc<br>md  |            |        |        |      |      |       |           |        | /BUSY               | 0000h |

|       |              |            |        |        |      |      |       | SQDT<br>1 | SQDT0  |                     |       |

| 19    | SNScm<br>d   |            |        |        |      |      | SNS2  | SNS1      | SNS0   | **SIGNAL<br>MONITOR | 0000h |

|       |              |            |        |        |      |      |       | Ssel      |        |                     |       |

| 1A    | FLGcm<br>d   | stp        | Fptmg  | SSVon  | HOME | it∨j | TSV   | SSV       | enTJn  | *SERIAL<br>DATA     | 2021h |

|       |              | DFCTe<br>d | ATSCed | Tbmthd |      |      | FSend |           | enLOCK |                     |       |

| 1B    | SNSCc<br>md  | RWB        |        | NORM   | FTLK |      |       |           | BANK   | /BUSY               | -     |

|       |              | MOD7       | MOD6   | MOD5   | MOD4 | MOD3 | MOD2  | MOD1      | MOD0   |                     |       |

| 1C    | DPRWc<br>md  | DD11       | DD10   | DD9    | DD8  | DD7  | DD6   | DD5       | DD4    | *SERIAL<br>DATA     | -     |

|       |              | DD3        | DD2    | DD1    | DD0  | ST6  | DPS2  | DPS1      | DPS0   |                     |       |

| 1D    | FTSTc<br>md  |            |        |        |      |      |       |           |        | /BUSY               | -     |

|       |              |            |        |        | WTF  |      |       |           | WFF    |                     |       |

| 1E    | RamRc<br>md  | NEXT       | 0      | 0      | BANK | 0    | 0     | 0         | 0      | *SERIAL<br>DATA     | -     |

|       |              | RAM7       | RAM6   | RAM5   | RAM4 | RAM3 | RAM2  | RAM1      | RAM0   |                     |       |

| 1F    | RamWc<br>md  | RD15       | RD14   | RD13   | RD12 | RD11 | RD10  | RD9       | RD8    | /BUSY               | -     |

|       |              | RD7        | RD6    | RD5    | RD4  | RD3  | RD2   | RD1       | RD0    |                     |       |

| 20    | TTKcm<br>d   | LK15       | LK14   | LK13   | LK12 | LK11 | LK10  | LK9       | LK8    | /BUSY               | -     |

|       |              | LK7        | LK6    | LK5    | LK4  | LK3  | LK2   | LK1       | LK0    |                     |       |

Table 1. Servo part MICRO-CONTROLLER command set (Continued)

|       |              |            |             |       | Data   |       |            |           |       |       | INIT. |

|-------|--------------|------------|-------------|-------|--------|-------|------------|-----------|-------|-------|-------|

| Addr. | CMD          | D15        | D14         | D13   | D12    | D11   | D10        | D9        | D8    | Sense | Value |

|       |              | D7         | D6          | D5    | D4     | D3    | D2         | D1        | D0    |       |       |

| 21    | FTGcm<br>d   |            |             |       |        |       |            |           |       | /BUSY | -     |

|       |              |            |             |       |        | UP    | Tchg       | DWN       | Fchg  |       |       |

| 58    | RFMRc<br>md  |            |             |       |        |       |            |           | EQS   | /BUSY | 0000h |

|       |              | MC7        | MC6         | MC5   | MC4    | MC3   | MC2        | MC1       | MC0   |       |       |

| 59    | ADCKc<br>md  |            |             |       |        |       |            |           |       | /BUSY | 0000h |

|       |              | TZCSE<br>L | APCGAI<br>N |       |        |       |            |           | ADCK  |       |       |

| 5A    | RFBALc<br>md |            |             |       |        |       |            |           |       | /BUSY | 0010h |

|       |              | STSL1      | STSL0       |       | TBAL4  | TBAL3 | TBAL2      | TBAL1     | TBAL0 |       |       |

| 5B    | RFSTc<br>md  |            |             |       |        |       |            |           |       | /BUSY | 0000h |

|       |              | VISEL      | SF2         | RFB1  | RFB0   | LDON  | PSTZ<br>CB | EQL1      | EQL0  |       |       |

| 5C    | EFMSc<br>md  |            |             |       |        |       |            |           |       | /BUSY | 0000h |

|       |              | MODEC      | SPEAK       | ONOFF | DONOFF |       | FOKS       | DFCT<br>S | MIRRS |       |       |

| 5D    | RFRWc<br>md  |            |             |       |        |       |            |           |       | /BUSY | 0000h |

|       |              | RW3        | RW2         | RW1   | RW0    |       | RWT2       | RWT1      | RWT0  |       |       |

| 5E    | RFIGcm<br>d  |            |             |       |        |       |            |           |       | /BUSY | 0000h |

|       |              |            | FG2         | FG1   | FG0    |       | TG2        | TG1       | TG0   |       |       |

| 5F    | TPWMc<br>md  |            |             |       |        |       |            |           |       | /BUSY | -     |

|       |              | PWM7       | PWM6        | PWM5  | PWM4   | PWM3  | PWM2       | PWM1      | PWM0  |       |       |

## Table 1. Servo part MICRO-CONTROLLER command set (Continued)

\*SERIAL DATA : User can read the response of the command after SENSE goes high which means ready.

\*\*SIGNAL MONITOR : SENSE output can be used in order to monitor other signals such as TLK, ATSC, TZC, and so on.

|       |                |                |                 |               | Data            |                       |                |                       |             |       | INIT. |

|-------|----------------|----------------|-----------------|---------------|-----------------|-----------------------|----------------|-----------------------|-------------|-------|-------|

| Addr. | CMD            | D7             | D6              | D5            | D4              | D3                    | D2             | D1                    | D0          | Sense | Value |

| 60    | DPLLCTL<br>1   | WIDE           | -               | PGAIN         | DLFGAIN         | ROM1                  | COAT           | -                     | RETREF      | Z     | 00h   |

| 61    | DPLLCTL<br>2   | REF98[1:<br>0] |                 | REF[1:0]      |                 | MAXTG<br>AIN[1:0<br>] |                | CAPRA<br>NGE[1:<br>0] |             | Z     | F0h   |

| 62    | DPLLCTL<br>3   |                | DIVS1[1:<br>0]  |               | DIVP1[5:0]      |                       |                |                       |             | Z     | 56h   |

| 64    | DPLLCTL<br>5   |                |                 |               | MITEST[7:0<br>] |                       |                |                       |             | Z     | 00h   |

| 65    | DPLLCTL<br>6   | CMDSPL<br>T    | PONLY           |               | MRANGE[1<br>:0] | FSREG                 | PLLTES<br>T    | PLLPW<br>RDN          | -           | Z     | 00h   |

| 70    | DBB            | -              | -               | -             | -               | TST1                  | -              | MAX                   | DBB         | Z     | 00h   |

| 80    | ESPMS          | MSWREN         | MSWAC<br>L      | MSRDEN        | MSRACL          | MSDCN<br>2            | MSDCN<br>1     | WAQV                  | MSON        | Z     | 00h   |

| 83    | AUDCNT<br>L1   | ATT            | MUTE            | SOFT          | NS              | CMP12                 | -              | -                     | -           | Z     | 00h   |

| 84    | ATTLEV<br>EL   | K7             | K6              | K5            | K4              | K3                    | K2             | K1                    | K0          | Z     | 40h   |

| 85    | OPTIONS<br>ET1 | RAMS1          | RAMS2           | -             | -               | COMPF<br>B            | COMP6<br>B     | COMP5<br>B            | COMP4B      | Z     | 04h   |

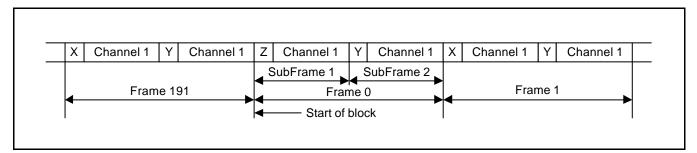

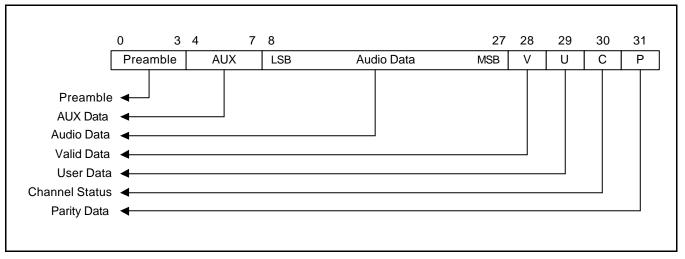

| 86    | DAUDIF         | CP1            | CP2             | LBIT          | DIT             | -                     | -              | -                     | -           | Z     | 00h   |

| A0    | FUNCNT<br>L    | CDROM          | ESPEN           | DEEM          | ERAOFF          | C1PNT                 | DBBON          | EMPHS<br>EL           | JITM        | Z     | 20h   |

| A1    | FSYNCN<br>TL   | FSEL[1:0<br>]  |                 | WSEL[1:<br>0] |                 | FSMD[1<br>:0]         |                | -                     | -           | LKFS  | 00h   |

| A2    | MODECN<br>TL1  | PWRDNL         | ESPDN           | SVOPDL        |                 | CLVEM<br>ERG          | EMERG<br>P     | NCLV                  | CRCQ        | Z     | e1h   |

| A3    | MODECN<br>TL2  | EFMSEL         | -               | -             | -               | -                     | -              | YFLAG                 | JTFRV       | Z     | 00h   |

| A8    | OUTCNT<br>L1   | -              | PLCK<br>MUTE    |               | WFCK<br>MUTE    | -                     | DAO<br>MUTE    | SBDT<br>MUTE          | C4M<br>MUTE | Z     | 00h   |

| A9    | OUTCNT<br>L2   | -              | MNTSEL[<br>2:0] |               |                 | -                     | -              | SC1                   | SC0         | Z     | 00h   |

| AA    | OUTCNT<br>L3   | -              | -               | -             | -               |                       | FREQS[<br>3:0] |                       |             | Z     | 00h   |

# Table 2. CD-DSP/ESP part Micro-Controller command set (Micro-Controller Write Command)

|       |              |        |      |                   | Data             |                       |                |              |            |        | INIT. |

|-------|--------------|--------|------|-------------------|------------------|-----------------------|----------------|--------------|------------|--------|-------|

| Addr. | CMD          | D7     | D6   | D5                | D4               | D3                    | D2             | D1           | D0         | Sense  | Value |

| AB    | AUDCNT<br>L2 | AMUTE  | ZCMT | -                 | ATTN             | FLAG2<br>V            | -              | DATXM<br>UTE | DACMUTE    | S0S1   | 81h   |

| B0    | TEST1        | DION   | -    |                   | TMODE[5:0<br>]   |                       |                |              |            | Z      | 00h   |

| C0    | DATTN        | -      | -    |                   | DATTN[5:0<br>]   |                       |                |              |            | Z      | 00h   |

| C1    | DACCNT<br>L  | ZDENL  | -    |                   | FSEMPH[1:<br>0]  | DACCL<br>K            | -              | BISTON<br>P  | TSEL       | Z      | 00h   |

| EO    | CLVGAI<br>N  | -      | WBN  | WPN               | RFCKSEL          | -                     | WB             | WP           | GAIN       | Z      | 07h   |

| E1    | CLVMOD<br>E  | UNLOCK |      | CLVIDLE           | PCEN             | СМЗ                   | CM2            | CM1          | CMO        | /CLVST | 00h   |

| E2    | CLVCNT<br>L1 | STRIO  | SMM  | PME               | SME              | PCKSE<br>L[1:0]       |                |              | PGAIN[1:0] | Z      | 02h   |

| E3    | CLVCNT<br>L2 | LC     | PML  | SML[1:0]          |                  | POS                   | SGAIN[<br>2:0] |              |            | Z      | 02h   |

| E4    | CLVCNT<br>L3 |        |      |                   | POFFSET[<br>7:0] |                       |                |              |            | Z      | 00h   |

| E5    | CLVCNT<br>L4 | SPLUS  | SDD  | PHASEDI<br>V[1:0] |                  | SMOFF<br>SET[3:0<br>] |                |              |            | Z      | 00h   |

| E6    | CLVCNT<br>L5 |        |      |                   | SOFFSET[<br>7:0] |                       |                |              |            | Z      | 00h   |

| F0    | PLAYCN<br>TL | -      | -    | -                 | -                | -                     | DASPE<br>ED    | DS1          | DS0        | Z      | 00h   |

## Table 2. CD-DSP/ESP part Micro-Controller command set (Micro-Controller Write Command) (Continued)

## Table 2. CD-DSP/ESP part Micro-Controller command set (Micro-Controller Write Command) (Continued)

| Addr. | CMD     |      | Data |      |      |     |     |     |     |     |     | Sense |     |   |

|-------|---------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-----|---|

| 87    | SUBQDAT | QAD3 | QAD2 | QAD1 | QAD0 | QD7 | QD6 | QD5 | QD4 | QD3 | QD2 | QD1   | QD0 | Z |

## Table 3. CD-DSP/ESP part Micro-Controller command set (Micro-Controller Read Command)

| Addr. | CMD       | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0   |

|-------|-----------|-------|-------|-------|-------|-------|-------|-------|------|

| 90    | ESPMEMST1 | FLAG6 | MSOVF | BOVF  |       | DCOMP | MSWIH | MRSIH |      |

| 91    | ESPMEMST2 | MSEMP | OVFL  | ENCOD | DECOD | QRDY  |       |       |      |

| Addr. | CMD       | D15   | D14   | D13   | D12   | D11   | D10   | D9    | D8   |

|       |           | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0   |

| 92    | MEMRESIDU | AM21  | AM20  | AM19  | AM18  | AM17  | AM16  | AM15  | AM14 |

|       |           | AM13  | AM12  | AM11  | AM10  | AM09  | AM08  | AM07  | AM06 |

## DIGITAL SERVO MICRO-CONTROLLER COMMAND DESCRIPTIONS

This digital servo signal processor (DSSP) is a CD-only optical pickup system servo command. This LSI was developed to simplify the hardware through automatic control and digital filter. However, manual control commands are also included to be comprehensive, and those could make somewhat complex command table. It was simplified as much as possible through the use of defaults.

Basically, SENSE = "L", when S5L9232 receives commands from the MICRO-CONTROLLER, and SENSE = "H" when the command job ends. The SENSE output is usually assigned /BUSY, but some commands assign different definitions to SENSE. In particular, when there is no SENSE related comments, S5L9232 recognizes SENSE = /BUSY.

The commands can be divided largely into two types, executable commands and non-executable commands (setting/reference commands). The former types are the action commands that directly execute servo-related operations and the latter are filter coefficient setting/reference commands, initialization commands and system constant/time setting/reference commands. Action commands have codes below 05h. If any one of these commands is executed, repeat jump is cancelled. For some commands, the previous command should be saved when the commands are inserted, since the commands are affected by the previous command

There are various types of command data, namely the coefficient data length, from 0 — 16 bits depending on each command. Please refer the following digital servo command specification.

S5L9232 supports only the MSB first micro-controller command input format. In the micro-controller command table, Italics means active low; '0' specified locations must be set to '0' when the command is used, and empty location is defined as 'don't care.'

#### STPcmd (Address 00H)

The STPcmd stops the execution of JMPcmd (05H) or automatic adjustment related servo operations, or changes the operations to the STOP mode. It also reduces the operating speed of embedded digital signal processor to save power consumption, turns on/off the laser diode, and clears the control/measurement data. The following descriptions of 4bit constant data are assigned.

| Name   | code |     |     |     | D   | Н   |      |      |      |

|--------|------|-----|-----|-----|-----|-----|------|------|------|

|        |      | D15 | D14 | D13 | D12 | D11 | D10  | D9   | D8   |

|        |      |     |     |     |     |     |      |      |      |

| STPcmd | 00   |     | DL  |     |     |     |      |      |      |

|        |      | D7  | D6  | D5  | D4  | D3  | D2   | D1   | D0   |

|        |      |     |     |     |     | LDX | IDLE | ABRT | STOP |

| .STOP | <ul> <li>Stop Mode. This command can be activated in any mode. This command reserve the STOP until the MON signal turns off. However, if the STOPcmd (0080H) is re-executed while STOP is being reserved, it immediately executes the STOP regardless of the MON condition.</li> <li>"0" : No execution. Executes next(ABRT) bit check.</li> <li>"1" : Reserves the STOP mode.</li> </ul> |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .ABRT | <ul> <li>Stops track searching and automatic control operation and returns to the previous state</li> <li>"0" : No execution. Executes IDLE bit check.</li> <li>"1" : Stops the jumping and control and returns to the previous state</li> <li>This command should not be used with 11h, 14h, 15h commands. We recommend that 11h, 14h,</li> </ul>                                        |

| .IDLE | <ul> <li>15h command be used with STOP(D8) for the same operation.</li> <li>: Sets to the IDLE (POWER SAVE MODE). RAM DATA remains.</li> <li>"0" : Returns to normal mode from the idle mode.</li> <li>"1" : Sets to IDLE MODE.</li> </ul>                                                                                                                                                |

| .LDX  | : Turns the laser diode on and off.<br>"0" : Laser diode off<br>"1" : Laser diode on                                                                                                                                                                                                                                                                                                      |

The priority order of the data bits is STOP, ABRT, and IDLE and LDX are equal priority. If the higher priority bits are "1", the IDLE and LDX bits are not checked.

All RAMs are cleared only when STOP=ABRT = 1. Although the RAM can be cleared using the normal STPcmd, in this case, the automatically controlled value and measurement are not cleared so that the servo can be immediately turned on without re-control in the next play. However, if the disc is changed, these values must be cleared. Because it is best to start from the beginning when the disc is changed, the control values should be cleared using the STPcmd options.

In the IDLE mode, the embedded digital signal processor's speed becomes 1/256, reducing the power consumptions. The IDLE and LDX bits can be accepted only when the servo is off.

If another action command is to be used before the execution of the automatic control command completes, the command must be first aborted using the STPcmd.

#### **DDTcmd (Address 01H)**

The DDTcmd checks for the presence of the disc and outputs the result, and it simultaneously measures the offset. It can also control both the focus error input gain and focus balance.

Before it performs the focus search, it automatically turns on the laser diode. The auto mode, which automatically uses the triangular waveform, and MICRO-CONTROLLER manual mode can be used for the focus search. The speed is controlled through FPS2 — 0 in either mode.

The focus actuator should be moved faster during disc detection compare with focus pull-in to determine if the disc is present. (The focus is not pulled-in.) It can read the data that indicates the type and presence of the disc.

| Name   | code |      |      | DH   |      |     |      |      |      |  |  |  |  |

|--------|------|------|------|------|------|-----|------|------|------|--|--|--|--|

|        |      | D15  | D14  | D13  | D12  | D11 | D10  | D9   | D8   |  |  |  |  |

|        |      |      |      |      |      |     |      |      |      |  |  |  |  |

| DDTcmd | 01   |      | DL   |      |      |     |      |      |      |  |  |  |  |

|        |      | D7   | D6   | D5   | D4   | D3  | D2   | D1   | D0   |  |  |  |  |

|        |      | AUTO | UPDN | FIGA | FBAL | RPT | FSP2 | FSP1 | FSP0 |  |  |  |  |

| ./AUTO ./UF | PDN : sets focus search mode.                                                                    |

|-------------|--------------------------------------------------------------------------------------------------|

|             | 0 0 : Auto mode. SENSE output indicates busy(L)/ready(H).                                        |

|             | 0 1 : Auto mode. Automatically executes to focus pull-in DDTcmd's search                         |

|             | 1 0 : Manual up mode(actuator up). Actuator(FZC) signal is output through SENSE.                 |

|             | 1 : Manual down mode(actuator down). Actuator(FZC) signal is output through SENSE.               |

| ./FIGA      | : The Focus input gain is changed by the FE peak level. Because the input gain reference changes |

|             | in every control, control must be completed with one try.                                        |

|             | "0" : Control                                                                                    |

|             | "1" : No control (maintain previous gain)                                                        |

| ./FBAL      | : Controls F-BAL so that the minimum focus S-curve value and the absolute value of its maximum   |

|             | value becomes the same at DDTcmd.                                                                |

|             | "0" : Control                                                                                    |

|             | Fbal=FBk*(FEmax+FEmin) or Fbias=(FEmax+FEmin)/Fbmthd according to (FLGcmd)                       |

|             | "1" : No control (maintain previous balance)                                                     |

| .RPT        | : Controls the number of Actuator's UP/DOWN searches                                             |

|             | (when triangular waveform for the search is generated.)                                          |

|             | "0" : Search only once.                                                                          |

|             | "1" : REPEAT SEARCH (continues until the next command is input. However, SENSE                   |

|             | becomes 'H" when the 1st run ends.)                                                              |

| .FSP2 .FSP  | 1.FSP0 : Bit that controls the DDTcmd and Focus pull-in actuator speed(slope).                   |

|             | 0 0 0 : 2Hz (fast)                                                                               |

|             | 0 0 1 : 1Hz                                                                                      |

|             | 0 1 1 : 1/2Hz                                                                                    |

|             | 1 1 1 : 1/3Hz (slow) * Other settings are impossible.                                            |

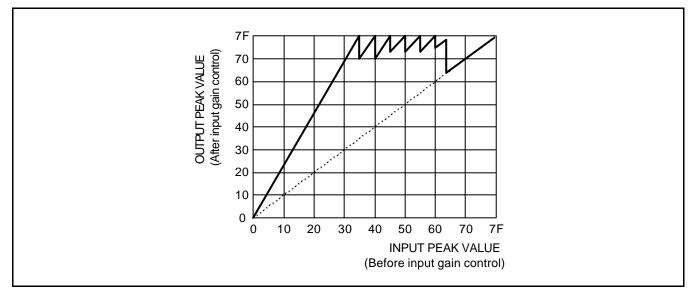

#### \* Focus input gain control

Manual and auto control methods are used for focus input gain control. The manual setting is recommended because of the unstable change in the FE peak signal, which is characteristics of the pickup. If the auto input gain control is chosen, the lookup table can be used to control the FEpk(00 — 7FH), measured during disc detection, according to the size of FEpk so that the value becomes approximately 80% of the 8bit ADC full range (7FH). This can be set with direct port write command (1Ccmd:DPRWcmd) in the manual control method. Note, when the tracking balance is controlled in the off-track state using the auto control method, TEpk can be extracted from the first TZC component of TE to control tracking so that it equals the focus.

#### \* Focus search

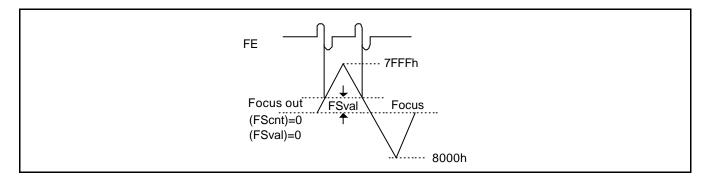

## Focus out =(FScnt+FSval)\*(FSpk)

If (FScnt)n = (FScnt)n-1  $\pm$  K (set K=3 in DDTcmd) for every M times, determined by FSP2 — 0, where M = 2m (the number of 1s of the m = FPS bit), fSRCH = fS/(2\*216\*M\*K-1). where 2\*216 is doubling the value since FScnt for 1 search cycle changes 0000h  $\rightarrow$  7FFFh  $\rightarrow$  0000h  $\rightarrow$  8000h  $\rightarrow$  0000h.

| Register | Addr. | Function                                                   | Default | Value  |

|----------|-------|------------------------------------------------------------|---------|--------|

| FSpk     | 0055h | Output control coefficient at F-srch pull in(full swing %) | 4000h   | 50%    |

| unBal    | 004Fh | S-curve unbalance determination % reference                | 2003h   | 25%    |

| DDT_J    | 0092h | Disc presence determination level                          | 1000h   | 150mVp |

| NZM      | 0093h | Noise level determination reference                        | 0800h   | 75mVp  |

## - DDT(Disc detect) Command Response format

| 15            | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0 |

|---------------|---|---|---|---|---|---|---|-----|---|

| FE PEAK LEVEL |   | 0 | 0 | 0 | 0 | 0 | 0 | DIN | Х |

.FE PEAK LEVEL : S-curve peak level

| .DIN | : DISC | C presence |  |

|------|--------|------------|--|

|      | "0"    | : No disc  |  |

|      |        | _          |  |

|   | "1"       | : Presence |

|---|-----------|------------|

| Х | : Don't d | care       |

#### FONcmd (Address 02H)

The FONcmd command turns the focus pull-in and tracking servo off. It automatically turns on the laser diode and selects from various forms of the pull-in method depending on the data accepted by the command. If the focus has already been turned on prior to the arrival of this command, nothing is executed. Furthermore, if FONcmd comes after TONcmd (03H), it turns on only the tracking servo.

| Name   | code |      | DH    |      |      |      |      |      |  |

|--------|------|------|-------|------|------|------|------|------|--|

|        |      | D15  | D14   | D13  | D12  | D11  | D10  | D9   |  |

|        |      |      |       |      |      |      |      |      |  |

| FONcmd | 02   |      |       |      | D    | L    |      |      |  |

|        |      | D7   | D6    | D5   | D4   | D3   | D2   | D1   |  |

|        |      | LYRX | Fmthd | FOPI | FSPC | PIL3 | PIL2 | PIL1 |  |

• It turns on the focus loop filter when the AUTO bit of DDTcmd(01H) is '1'.

```

.LYRX

: Assigns the focus search(pull-in) direction.

: Pulls-in from the bottom.

"1"

"0"

: Pulls-in from the top.

: Assigns the focus pull-in method.

.Fmthd

"0"

: Pulls-in from the top and bottom of the S-curve.

"1"

: Pulls -in either from the top or from the bottom of the S-curve.

./FOPI

: Determines whether retrying pull-in should be within the search ranges(FSrng) at focus drop.

"0"

: Auto mode (DSSP automatically tries to pull-in at focus drop)

"1"

: Does not try to pull-in again. That is, MICRO-CONTROLLER uses the FONcmd to pull-in.

: Automatic speed control bit at focus pull-in (This function reduces the search speed

.FSPC

as the search comes closer to the pull-in point)

"0"

: No automatic speed control (during search )

"1"

: Automatic speed control (Reduces the search speed by half following the S-curve)

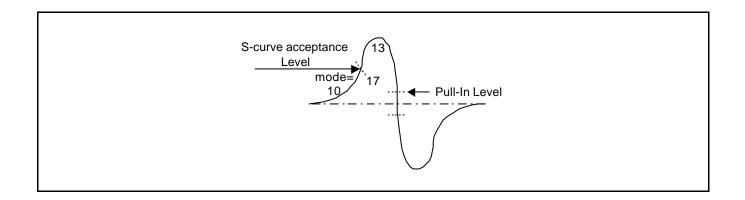

.PIL3, PIL2, PIL1, PIL0 : S-curve acceptance level : pull-in level

1

1

FEpk/2

:

FEpk/4

Х

Х

2

FEpk/2

FEpk/8

х

х

0

1

:

:

1

1

0

FEpk/4

FEpk/8

х

÷

:

0

1

0

FEpk/4

FEpk/16

:

:

х

```

FEpk/8

FEpk/8

:

:

FEpk/16

FEpk/32

1 x

0

х

0 0

0

0

2

:

D8

D0 PIL0

| Register | Addr. | Function                                                 | Default | Value |

|----------|-------|----------------------------------------------------------|---------|-------|

| FSpk     | 0055h | F-srch pull in output control coefficient (% full swing) | 4000h   | 50%   |

| FLoff    | 007Eh | FLKB (Focus lock) off time                               | 0172h   | 4.4ms |

| FLon     | 007Fh | FLKB (Focus lock) on time                                | 000Ah   | 113us |

| Fsrng    | 0091h | Focus re- pull-in search range                           | 5000h   | 737mV |

#### TONcmd (Address 03H)

TONcmd is the tracking pull-in command, which sets gains in the lens brake and track search mode. There is no operation if tracking is already on when this command arrives.

| Name   | code |     | DH   |     |      |      |      |      |    |

|--------|------|-----|------|-----|------|------|------|------|----|

|        |      | D15 | D14  | D13 | D12  | D11  | D10  | D9   | D8 |

|        |      |     |      |     |      |      |      |      |    |

| TONcmd | 03   |     | DL   |     |      |      |      |      |    |

|        |      | D7  | D6   | D5  | D4   | D3   | D2   | D1   | D0 |

|        |      |     | SLSV |     | TOLB | MTLB | SFOG | STRG |    |

| ./SLSV | : Sets sled servo on.                                                                 |

|--------|---------------------------------------------------------------------------------------|

|        | "0" : Turns on both tracking and sled servos on at the same time.                     |

|        | "1" : Does not turn on the sled servo (The sled command turns it on .)                |

| .TOLB  | : Sets the lens brake when the tracking servo is turned on.                           |

|        | "0" : Does not turn on the Lens brake.                                                |

|        | "1" : Turns on the lens brake until there is no MIRR signal.                          |

| .MTLB  | : Manual tracking lens brake                                                          |

|        | "0" : Does not turn on the Lens brake                                                 |

|        | "1" : Turns on the Lens brake(Turns on the lens brake when there is MIRR/TZC signal.) |

| .SFOG  | : Sets (kick+brk+GuT interval) focus gain during search                               |

|        | "0" : Does not change the gain.(manual)                                               |

|        | "1" : Automatically changes the gain.(down: changes to temporary gain.)               |

| .STRG  | : Sets the tracking gain when search ends (kick+brk+GuT+dlyTG interval).              |

|        | "0" : Does not change the gain.(manual)                                               |

|        | "1" : automatically changes the gain.(up: changes to temporary gain.)                 |

|        |                                                                                       |

| Register | Addr. | Function                                      | Default | Value  |

|----------|-------|-----------------------------------------------|---------|--------|

| GuT      | 0077h | Track gain up time after jump (Track pull-in) | 0400h   | 11.6ms |

| dlyTG    | 0079h | TGup delay time after Gut ends                | 0200h   | 5.5ms  |

| TLoff    | 0080h | TLKB off delay time setting                   | 0001h   | 11.3us |

| TLon     | 0081h | TLKB on delay time setting                    | 0100h   | 2.9ms  |

#### SLDcmd (Address 04H)

This command controls the sled motor. The bit is checked from the HOMEIN bit. It moves the pickup in the both directions (from inside to outside and from outside to inside) and turns on and off the sled servo. The MICRO-CONTROLLER controls the sled movement during play. The sled can also be moved manually. It can also extract the home location.

| Name   | code |     | DH   |     |     |     |      |      |        |

|--------|------|-----|------|-----|-----|-----|------|------|--------|

|        |      | D15 | D14  | D13 | D12 | D11 | D10  | D9   | D8     |

|        |      |     |      |     |     |     |      |      |        |

| SLDcmd | 04   |     | DL . |     |     |     |      |      |        |

|        |      | D7  | D6   | D5  | D4  | D3  | D2   | D1   | D0     |

|        |      |     |      |     |     |     | SPLY | SMOV | HOMEIN |

.HOMEIN : Set SLED HOMEIN MODE (priority Bit)

- "0" : Off(Checks the upper bits.)

- : After returning to the home location, specified time: tHFwd, it moves to the outside. SENSE = *BUSY*/READY

.SMOV, SPLY : Bit that controls the sled servo on/off and sled movement

- 0 0 : Sled servo off/ move off

- 0 1 : Sled servo on

- 1 0 : Sled forward move(in -> out). Sets the kick level to LEScmd's 'SKCKd'.

- 1 1 : Sled backward move(out -> in).Sets the kick level to LEScmd's 'SKCKd'.

- Even after home in, kick more inwards during the specified time:tHBwd.

(only when the focus servo is off).

.DH4 — 0 : Don't care

"1"

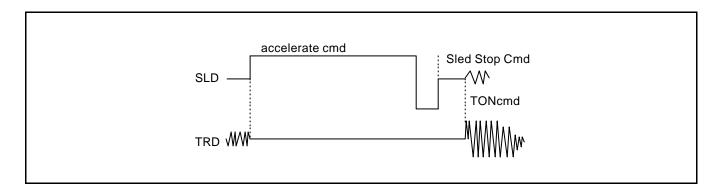

It operates with SENSE = *BUSY*/READY when the focus servo is off. On the other hand, when the focus servo is on, SENSE becomes manual sled move. If OKScmd's Cout is "0", TZC signal is output through SENSE and, if not, ( $\neq 0=2n$ ) track count busy signal is output through SENSE. Then, the MICRO-CONTROLLER counts these signals to move the sled. First OKScmd sets Cout; FONcmd turns off tracking; and then the SLDcmd accelerates the sled. When the number of SENSE signals nears the objective count, the SLDcmd brakes the sled. Then, when the interval between the SENSE signals are wide apart to consider the sled to have stopped, the SLMcmd turns off the brake pulse. After safe standby, it sends the track on command:TONcmd to turn on the tracking and sled servos to return to play.

| Register | Addr. | Function                          | Default | Value  |

|----------|-------|-----------------------------------|---------|--------|

| SKCKd    | 008Ch | SLED kick level(Vref reference)   | 7000h   | 1049ms |

| tHBwd    | 0056h | After home in, backward move time | 1833h   | 70ms   |

| tHFwd    | 007Bh | After home in, fwd move time      | 0F00h   | 43.3ms |

#### JMPcmd (Address 05H)

The JMPcmd executes the track search. There are two types of search methods, track jump a sled move. With this command, repeated search is possible. The manual mode is available for track jump.

| Name   | code        |             | DH   |      |      |      |      |      |      |

|--------|-------------|-------------|------|------|------|------|------|------|------|

|        |             | D15         | D14  | D13  | D12  | D11  | D10  | D9   | D8   |

|        |             | DIR         | JPM1 | JPM0 | JIT2 | JIT1 | JITO | JPD9 | JPD8 |

| JMPcmd | 05          |             | DL   |      |      |      |      |      |      |

|        |             | D7          | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|        |             | JPD7        | JPD6 | JPD5 | JPD4 | JPD3 | JPD2 | JPD1 | JPD0 |

|        | ets the jum | n direction |      |      |      |      |      |      |      |

.DIR : Sets the jump direction

"0" : Forward (outward) jump

"1" : Reverse (inward) jump

.JPM1 — 0 : Jump type assignment bit

"00" : Automatically determines whether to perform a track jump or sled jump depending on the number of jump tracks. The type of jump is determined by the boundary value:BOUND set by OKScmd.

"01" : Executes tracking jump

"10" : Executes sled move.

"11" : Repeats the track jump for every interval set in  $JIT_{2-0}$  (interval jump)

.JIT2 — 0 : Bit that sets the time interval of the repeated track jump. The period is the time from the initial jump time to the initial time of the next jump.

| JIT2 ¾ 0 | Time interval (repeat cycle) | Comment |

|----------|------------------------------|---------|

| 000      | Reserved                     |         |

| 001      | 2.7Hz                        |         |

| 010      | 5.4Hz                        |         |

| 011      | 8.1Hz                        |         |

| 100      | 13.5Hz                       |         |

| 101      | 21.6Hz                       |         |

| 110      | 29.7Hz                       |         |

| 111      | 40.5Hz                       |         |

<sup>.</sup>JPD12 — 0 : When the JPM1 — 0 bit is set to something besides "11", JIT2 — 0 becomes JD12 — 10. : When JPM1 — 0 bit is set to "10", the track number + 8 set by JD12 — 0 is the number of tracks to be jumped.

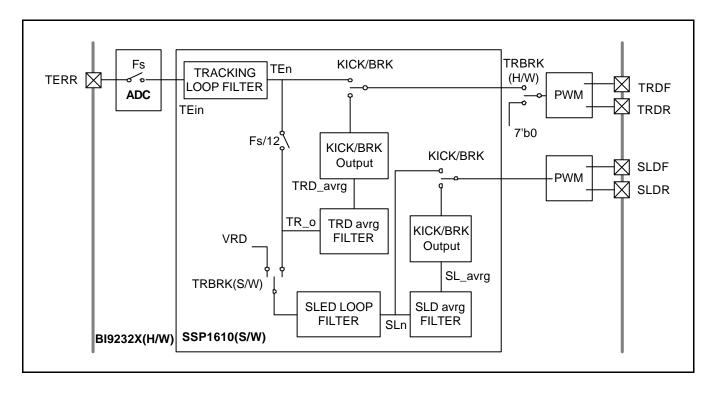

It reads in the lens brake on/off signal, which is created by the H/W, through the status register into SSP1611\_CDP(Digital signal processor) to brake the sled output with the lens brake after a track jump. After it reads in the signal, then it substitutes the sled filter input (TR\_o) data with '0' using software when the lens brake turns on. To do this, the 'SLbrk' bit must be set to '1' using the HDWcmd just after initializing the IC.

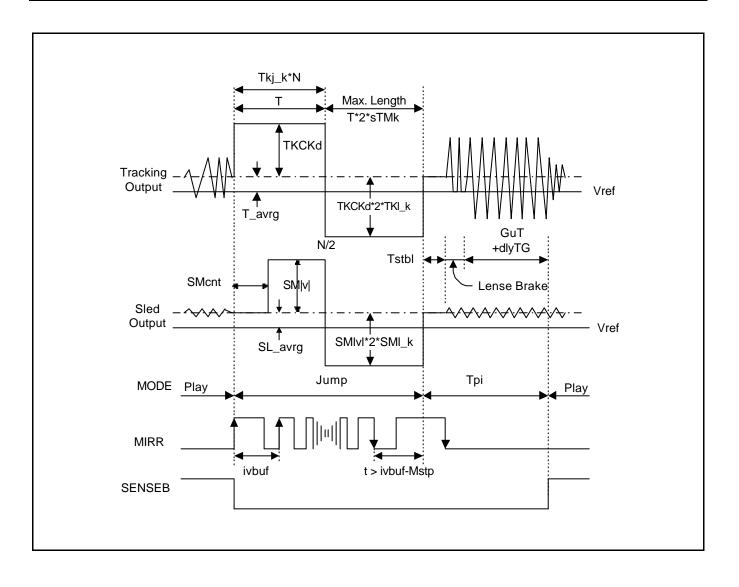

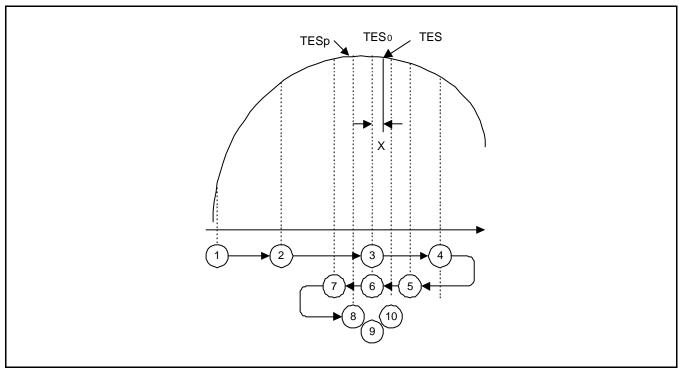

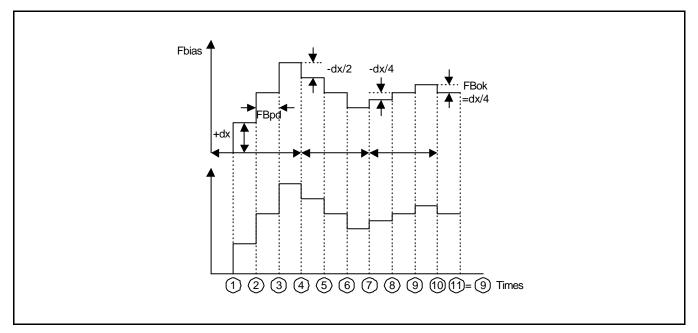

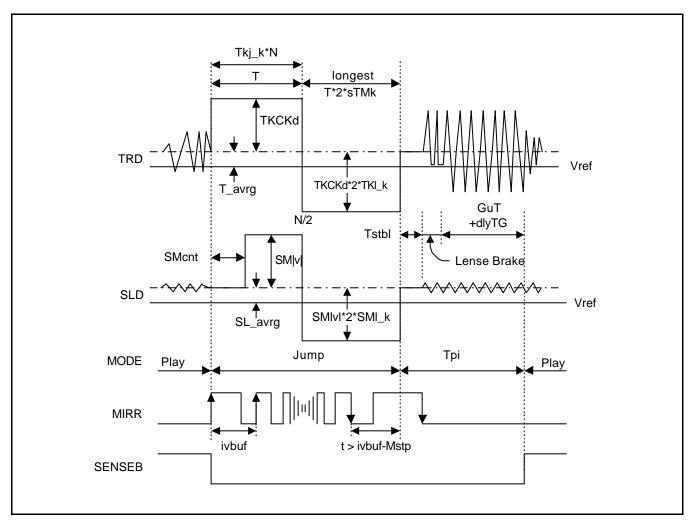

The kick level (TKCKd) was superposed onto the pre-jump average TRD output (TRD\_avg) to generate the trk kick pulse, which was output through the TRD. If the track counter (H.CT) become half the count value (GSkbf) by jumping (N)\*TKj\_k trk, the brake turns on and this level becomes TKCKd\*2\*TKl\_k times the original level. Jump direction is changed to the reverse direction if the level is less than the trk end condition at the MIRR reverse point during the brake interval. If this occurs, pickup can return to the location before the jump or pull-in can become unstable due to the sharp deceleration intervals. Therefore, the kick time (T)\*2\*sTMK is suggested for the maximum brake time to prevent sharp energy fluctuation between acceleration and deceleration.

If the number of tracks to move from the track kick reaches the sled move count (SMcnt), the sled move level (SMlvl) kick is superposed onto the pre-jump average sled output (SL\_avrg) and the level becomes SMlvl\*2\*SMl\_k as track kick and sled changes to brake. The kick/brake interval limit shares the tracking setting condition, except that SMcnt does not move the sled, but specifies the number of usable track range to jump only using the lens. The track pull-in (Tpi\_int) routine actually starts to run after the stabilization time. \_After the Tstbl ends, the GuT is set to tracking gain up (when STRG=H); however, GuT continues to reload if lens brake (MIRR) exists. Therefore, after the period from the end of lens brake to the end of the GuT period ends, first of all, the focus gain down from the beginning of the jump is returned to normal. Then, after dlyTG time passes, tracking gain is also returned to normal, after which it returns to the normal play mode. Converting time of focus gain and that of tracking gain are different each other by dlyTG. The reason is for preventing the system from emergency situation such as tracking oscillation and focus drop which are resulted from the tracking gain conversion under the unstable focusing on converting or right after transition characteristics for focus gain. If the maximum deceleration period does not end at window(T\*2\*sTMk) : t < ivbuf-Mstp, it can return to over-acceleration (BRK) making it unstable. Therefore, the maximum brk time has been set.

| Register | Addr. | Function                                                                                       | Default | Value   |

|----------|-------|------------------------------------------------------------------------------------------------|---------|---------|

| TKCKd    | 008Bh | initial kick level                                                                             | 1800h   | 224.8mV |

| SMIvI    | 008Eh | Trk jump sled move level                                                                       | 7000h   | 1032mV  |

| Tkj_k    | 0024h | Kick/brk duty setting coefficient                                                              | 3D00h   | 47.70%  |

| TKI_k    | 0026h | Trk brake level control coefficient                                                            | 1000h   | 26.2%   |

| SMI_k    | 0027h | Sled brake level control coefficient                                                           | C000h   | -100%   |

| SMbrkl   | 0028h | Brake level when sled move                                                                     | 0008h   | 0.00V   |

| fsTjN    | 00BAh | Forced Brk control trk number                                                                  | 0003h   | 3trk    |

| sTMk     | 00DAh | Trk brake interval detection window time Note1)                                                | 4000h   | 50.0%*2 |

| LbT      | 0072h | Lens brake start time                                                                          | 0078h   | 1.35ms  |

| Tstbl    | 0074h | Stabilization time after Trk jump                                                              | 0000h   | 0us     |

| Twin     | 0075h | MIRR/TZC blind time                                                                            | 000Ah   | 113us   |

| Mstp     | 0076h | Jump stop time compensation time(stop=ivbuf-Mstp)                                              | 0003h   | 33.9us  |

| GuT      | 0077h | Tgup delay time after jump end                                                                 | 0400h   | 11.6ms  |

| Jstp     | 0078h | Stop when "Tracking jump stop timer <mirr cycle"<="" td=""><td>0018h</td><td>271ms</td></mirr> | 0018h   | 271ms   |

| dlyTG    | 0079h | Delay time after GuT end                                                                       | 0200h   | 5.5ms   |

| tJap     | 007Ah | Jump assist procedure time(enMH=SLST=0)                                                        | 024Ch   | 79.7ms  |

| Cchg     | 0086h | Cout(up/dn) and TZC/MIRR(up) select track number                                               | 0080h   | 128trk  |

| Bound    | 0087  | Trk jump and sled move boundary trk number                                                     | 0080h   | 128trk  |

| SMcnt    | 0088h | Trk number from after trk kick to sled move                                                    | 0001h   | 1trk    |

| SScnt    | 0089h | Brake when the remaining track number becomes less than SScnt when the sled moves              | 0200h   | 512trk  |

| Sbrk     | 005Bh | Sled move Brake max time                                                                       | 2380h   | 103ms   |

**NOTE:** the longest trk brk time = T \* 2 \* sTMk (T=kick time)

The finishing condition of jump is ivbuf-Mstp when INIcmd's BTS is 'L' and Jstp\_Mstp when BTS is 'H'. Before Twin, the TM1(Jump stop cycle (MIRR  $\downarrow$  to  $\downarrow$ ) detection down counter) is set to Jstp. After Twin, it is set to ivbuf or Jstp depending on the BTS.

## EMEcmd (Address 07H)

The EMEcmd command directs the defect/shock emergency processing.

| Name   | code | DH   |      |     |      |      |      |      |    |

|--------|------|------|------|-----|------|------|------|------|----|

|        |      | D15  | D14  | D13 | D12  | D11  | D10  | D9   | D8 |

|        |      |      |      |     |      |      |      |      |    |

| EMEcmd | 07   | DL   |      |     |      |      |      |      |    |

|        |      | D7   | D6   | D5  | D4   | D3   | D2   | D1   | D0 |

|        |      | Test | SLST |     | upFv | dsAS | ASFO | ASTR |    |

| .Test | : Sets filter test mode (Set by FTSTcmd.)                                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------|

| .SLST | "0" : Normal mode "1" : Filter test mode<br>: Bit that decides whether to stop the sled when the lock signal turns off. |

| .3131 | "0" : No STOP "1" : STOP                                                                                                |

| .upFv | : Specify whether or not to compensate the focus output offset: FSval when the focus pulls in.                          |

|       | <ul><li>"0" : No compensation (during the time measured in focus search)</li><li>"1" : Compensation</li></ul>           |

| .dsAS | : Specify whether or not to process the anti-shock.                                                                     |

|       | "0" : Enable. Validates ASFO, ASTR and ASBR functions.                                                                  |

|       | "1" : Disable. Leave it up to the servo.                                                                                |

| .ASFO | : Bit that decides on whether to down the focus gain in case of a shock                                                 |

|       | "0" : Maintains the focus gain to normal.                                                                               |

|       | "1" : Downs the focus gain.                                                                                             |